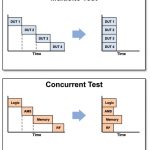

It requires lateral thinking in bringing new innovation into conventional solutions to age-old hard problems. While the core logic design has evolved adding multiple functionalities onto a chip, now called SoC, the structural composition of DFT (Design for Testability) has remained more or less same based on XOR-based compression… Read More

Tag: test

Auto Introspection

It is an indictment of our irrationality that our cars are now more health-conscious than we are. Increasingly safety-conscious readings of the ISO26262 standard now encourage that safety-critical electronics (anti-lock braking control for example) automatically self-test, not just at power-on but repeatedly as the car… Read More

Addressing Moore’s Law with the First Law of Real Estate: Location, location, location

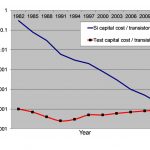

Design sizes and complexities have grown exponentially (it’s a Law!), and consequentially the task of silicon test has become proportionally more expensive. The cost of testing a device is proportional to the amount of test data that is applied, and therefore the time it takes, which in turn is proportional to both design size … Read More

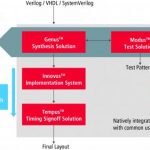

Saving Time and Money on Your Next SoC Project

Every SoC project that I know of wants to finish on time, under budget, and maximize profits per device. When I first started out doing DRAM design I learned that we could maximize profit by doing shrinks of existing designs, move from ceramic to plastic packages, and reduce the amount of time spent on a tester. Today, the economic … Read More

Don’t Miss Mentor Graphics U2U San Jose, April 21, 2015

Mentor Graphics’ User2User conference will be held next week on April 21[SUP]st[/SUP] at the San Jose DoubleTree Hotel. This one-day, free conference is the perfect opportunity to learn, network, and share with other Mentor Graphics users.

The day starts off with back-to-back keynotes that examine different aspects of the … Read More

More Test Points are Better

I got really involved in testability back at CrossCheck in the 1990’s when they designed a way for Gate Arrays to have 100% observability without any Design For Test (DFT) requirements on designers. The Japanese Gate Array companies loved this approach and their customers enjoyed the highest test coverage without being… Read More

Improve Test Robustness & Coverage Early in Design

In a semiconductor design, keeping the design testable with high test coverage has always been a requirement. However with shrinking technology nodes and large, dense SoC designs and complex logic structures, while it has become mandatory to reach close to 100% test coverage, it’s extremely difficult to cope with the explosion… Read More

What’s next in test compression?

If you’ll be at ITC TestWeek in Seattle (Oct 20-23), here’s one event you don’t want to miss: a technology reception hosted by Mentor, with Janusz Rajski and Nilanjan Mukherjee as the featured speakers. It is free to ITC attendees and you can register here. [If for some crazy reason you haven’t registered for ITC yet, do that… Read More

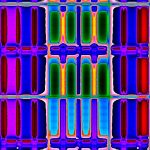

Layout-aware Diagnosis

Traditional test methodologies have been based on the functional model, that is to say the netlist. The most well-known is probably the stuck-at model which grades a sequence of test vectors by whether they would have managed to notice the difference between a fully functional design and one where one of the signals was permanently… Read More

One SPIE session not to miss

The time is nigh for another meeting of the practitioners of the lithographic arts, dark and otherwise, at the SPIE Advanced Lithography symposium.

I love this conference for the engagement you see, both in the sessions and in the hallways. People actually meet and talk and argue. There’s always interesting gossip, exciting technologies,… Read More