Networks-on-chip (NoCs) are very configurable, arguably the most configurable piece of IP that you can put on a chip. The only thing that comes close are highly configurable extensible VLIW processors such as those from Tensilica (Cadence), ARC (Synopsys) and CEVA but Sonics would argue their NoCs are even more flexible. But … Read More

Tag: test

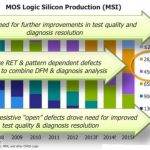

New Frontiers in Scan Diagnosis

As we move down into more and more advanced process nodes, the rules of how we test designs are having to change. One big challenge is the requirement to zoom in and fix problems by doing root cause analysis on test data alone, along with the rest of the design data such as detailed layout, optical proximity correction and so on. But without… Read More

Mentor Seminar: Evolution of diagnosis-driven yield analysis

It’s a fact that new process nodes come with some amount of yield challenges. One way to find and eliminate silicon defects is through diagnosis-driven yield analysis (DDYA), which is the topic of a free seminar by Mentor Graphics in Fremont this Thursday, October 10 from 11:30am – 2pm (yes, lunch is included because Mentor… Read More

SpyGlass: Focusing on Test

For decades we have used a model of faults in chips that assumes that a given signal is stuck-at-0 or stuck-at-1. And when I say decades, I mean it. The D-algorithm was invented at IBM in 1966, the year after Gordon Moore made a now very famous observation about the number of transistors on an integrated circuit. We know that stuck-at… Read More

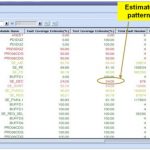

A Goldmine of Tester Data

Yesterday at SEMICON West I attended an interesting talk about how to use the masses of die test data to improve silicon yield. The speaker was Dr. Martin Keim, from Mentor Graphics.

First of all, he pointed out that with advanced process nodes (45nm, 32nm, and 28nm), and new technologies like FinFETs, we get design-sensitive defects.… Read More

Towards the 0 DPM Test Goal

At Semicon yesterday I attended Mentor’s presentation on improving test standards. Joe Sawicki was meant to present but he was unable to get a flight due to the ongoing disruption at SFO after last weekend’s crash. I just flew in myself and it is odd to see the carcase of that 777 just beside the runway we landed on.

The … Read More

DAC lunch seminar: Better IP Test with IEEE P1687

What: DAC lunch seminar (register here)

When: June 5, 2013, 11:30am – 1:30pm

Where: At DAC in lovely Austin, TX

Dr. Martin Keim of Mentor Graphics will present this overview of the new the IEEE P1687 standard, called IJTAG for ‘internal’ JTAG.

If you are involved in IC test*, you’ve probably heard about IJTAG. If you … Read More

Mentor Graphics’ Best User2User Ever

Calling all Mentor users! Don’t forget to register for the U2U in San Jose on Thursday, April 25.

In addition to three worthy keynotes, you will find a more interactive and solution-focused day than in the past. There are sessions on place & route, custom/AMS, emulation, test and yield analysis, functional verification, Calibre… Read More

IJTAG for IP Test: a free seminar

What: Better IP Test with IJTAG

When: 26 March, 2013, 10:30am-1:30pm

Where: Mentor Graphics, 46871 Bayside Parkway, Fremont, CA 94538

If you are involved in IC test*, you’ve probably heard about the IEEE P1687 standard, called IJTAG for ‘internal’ JTAG. IJTAG defines a standard for embedded IP that includes simple… Read More

Yield Analysis and Diagnosis Webinar

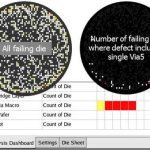

Sign up for a free webinar on December 11 on Accelerating Yield and Failure Analysis with Diagnosis.

The one hour presentation will be delivered via webcast by Geir Eide, Mentor’s foremost expert in yield learning. He will cover scan diagnosis, a software-based technique, that effectively identifies defects in digital logic… Read More