One of the benefits of being part of SemiWiki is building relationships with a wide variety of companies covering every semiconductor design application imaginable. We are blessed, absolutely. Another benefit of being part of SemiWiki are the invitations to attend, participate, and even organize events such as EDPS. Last year… Read More

Tag: synopsys

Sebastian Thrun: Self-driving cars, MOOCs, Google Glass and more

Sebastian Thrun gave a fascinating keynote at SNUG last week. It didn’t have that much to do with IC design but he discussed 3 projects that he had been involved with. Anyone would be happy to have just one of these projects on their resume but he has all these (and more).

The first is the Google self-driving car. This project actually… Read More

Book review: “shift left” with virtual prototypes

Shipping a product with complete software support at official release is a lot more difficult than it sounds. Inevitably, there is less than enough hardware to go around, and what little there is has to fill the needs of hardware designers, test and certification engineers, software development teams, systems integration teams,… Read More

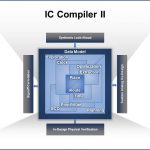

SNUG and IC Compiler II

I have been at SNUG for the last couple of days. The big announcement is IC Compiler II. It was a big part of Aart’s keynote and Monday lunch featured all the lead customers talking about their experience with the tool.

The big motivation for IC Compiler II was to create a fully multi-threaded physical design tool that will scale… Read More

AMS Verification and Regression Testing of SoC Designs

Digital verification engineers on SoC designs have adopted many techniques to help ensure first silicon success: using compiled simulators, constrained random test, simulation farms, SystemVerilog methodology, and self-checking testbenches. AMS verification has tended to be ad-hoc or sharply divided into separate analog… Read More

IC Implementation Tool Gets a Rewrite, Now 10X Faster

EDA start-up companies often have the advantage over established vendors by being able to start from scratch, instead of having to maintain some legacy code that no longer is competitive. But what happens when the established vendor decides to rewrite their IC implementation tools from scratch? In this case it’s good news,… Read More

SEMI Breakfast Forums: the Internet of Things

Coming up on April 10th is the SEMI Silicon Valley Breakfast Forum Internet of Things—Driving the Microelectronics Revolution. It runs from 7am to 10.45am and will be held at SEMI Headquarters which is at 3081 Zanker Road in San Jose.

Widespread adoption of the Internet of Things will take time, but the movement is advancing thanks… Read More

Dr. Walden Rhines Vision on Semiconductor & India

Last month India Electronics & Semiconductor Association (IESA) held its Vision Summit at Bangalore in which luminaries from across the semiconductor and electronics industry presented their views about the future of this industry and India’s progress. Dr. Walden C. Rhines, Chairman and CEO of Mentor Graphicspresented… Read More

Synopsys Announces Verification Compiler

Integration is often an underrated attribute of good tools, compared to raw performance and technology. But these days integration is differentiation (try telling that to your calculus teacher). Today at DVCon Synopsys announced Verification Compiler which integrates pretty much all of Synopsys’s verification technologies… Read More

Synopsys’s Next Generation Emulator, ZeBu Server-3

Since Synopsys acquired Eve over a year ago, they haven’t announced anything new in the ZeBu product line. Emulators are not like software where you expect incremental releases a couple of times per year, each new “release” is a complete re-design using new hardware fabric in a new process technology. Earlier… Read More