Tuesday morning at DAC I enjoyed a free breakfast courtesy of Synopsysand GLOBALFOUNDRIESwhere I learned more about the emerging market of IoT, and what it means to semiconductor, EDA and IP vendors. Panelists included: Semico Research, HP, Synopsys, GLOBALFOUNDRIES and Broadcom. … Read More

Tag: synopsys

AMS Panel: Micronas, Infineon, AMD, STMicro

Synopsyshosted an AMS Luncheon panel today at DACin the Westin Hotel and invited four customers to talk about their actual design challenges and experiences. I’ve typed up my notes from this event.… Read More

Synopsys @ #51DAC Must See!

Accelerating Innovation—that has been at the heart of Synopsys’ commitment to its customers for more than 25 years. As a leader in EDA and semiconductor IP, Synopsys’ software, IP and services help engineers address their design, verification, system and manufacturing challenges and accelerate their innovations. Since 1986,… Read More

Analog and Full Chip Simulation at Micron

IDM companies like Micronuse SPICE circuit simulators during the design phase in order to predict timing, currents and power on their custom IC chip designs at the transistor level. A senior memory design engineer at Micron named Raed Sabbahtalked today at a webinarabout how the embedded solutions group uses the FineSimcircuit… Read More

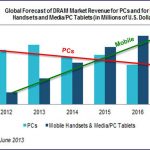

Intel is Still Missing Mobile!

Paul McLellan was on assignment in Hong Kong last week so I attended the Linley Mobile Conference and was not surprised Intel did not present. During the networking sessions I asked more than a dozen people why and the answers were pretty focused on “Intel still does not play well with others” and “Intel’s current mobile offerings… Read More

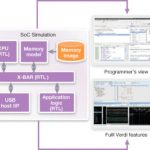

Hardware/Software Debug

One of the big challenges with modern SoCs is that they have a complex software component as well as the hardware itself being complex. Some aspects of the hardware can be debugged independently of the software and vice versa, but often it is not immediately clear whether the source of a problem is hardware, software or some interaction… Read More

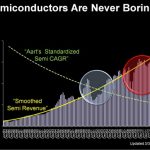

Designing Change into Semiconductor Techonomics

Every industry has famous thought leaders that can summarize where we’ve been and then paint a picture of where we’re headed towards in the future. Often they make statements that become industry expressions, like “Moore’s Law” or the “Internet of Things”. I think that if Synopsys… Read More

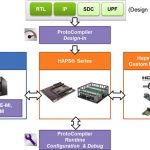

More knowledge, less time in FPGA-based prototyping

I recently published a post on LinkedIn titled “Sometimes, you gotta throw it all out” in reference to the innovation process and getting beyond good to better. A prime example has crossed my desk: the new ProtoCompiler software for Synopsys HAPS FPGA-based prototyping systems.

Last week, I spoke with Troy Scott, product marketing… Read More

Welcome, LPDDR4!

Thanks to memory controller expert Marc Greenberg, Marketing Director for DDRn Controller IP with Synopsys, for this post “Qualcomm announces first application processor with LPDDR4 capability”. According with Marc, this Application Processor, the Snapdragon 810, is “the first product that I’m aware of that will use LPDDR4… Read More

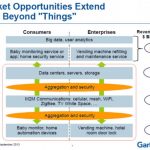

Will IoT Drive the Next Semiconductor Revolution?

To further my quest to comprehend the latest trends in the semiconductor industry continues, I spent the morning with SEMI at the “The Silicon Valley Breakfast Forum: Internet of Things (IoT) – Driving the Microelectronics Revolution” seminar. I’m a big fan of the breakfast seminar concept. I’m up early anyway and it is … Read More