The MIPI Alliance was founded in 2003 by large IDM to standardize chip-to-chip interfaces in the wireless phone (mobile) segment. The various MIPI specifications (CSI, DSI, DigRF and many more) have been adopted by the application processor chip makers (usually large IDM or fabless, like Intel or Qualcomm initially and many … Read More

Tag: synopsys

10nm Will Be an Epic Process Node!

In the history of the fabless semiconductor industry the foundries have always been a process node or two behind the leading semiconductor manufacturers. Starting in Q1 2017, for the first time in fabless semiconductor history, the foundries will have a process node advantage. This is horrible news for some but great news for … Read More

IC and System Design for Mobile and Wearable Devices!

The Linley Mobile and Wearable Conference is coming up so let’s take a look at what is in store for us. Bernard Murphy, Tom Simon, and I will be covering the event live for SemiWiki and we will also be doing a book giveaway/signing for our new “Prototypical” book (compliments of S2C Inc.) during the networking event on Tuesday evening.… Read More

Learn How to Debug UVM Test Benches Faster – Upcoming Synopsys Webinar

UVM for developing testbenches is a wonderful thing, as most verification engineers will attest. It provides abstraction capabilities, it encapsulates powerful operations, it simplifies and unifies constrained-random testing – it has really revolutionized the way we verify at the block and subsystem level.

However great… Read More

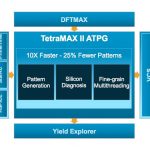

EDA Tool for ATPG – Refactor or Rewrite?

In the life of all EDA software tools comes that moment when new requirements make developers stop and ask, should I continue to refactor the existing code or just start all over from scratch using a new approach? Synopsys came to that junction point when ATPG run times were reaching days or even weeks on the largest IC designs, something… Read More

Circuit Simulation Panel Discussion at #53DAC

Four panelists from big-name semiconductor design companies spoke about their circuit simulation experiences at #53DAC in Austin this year, so I attended to learn more about SPICE and Fast SPICE circuit simulation. I heard from the following four companies:… Read More

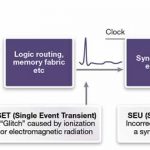

TMR approaches should vary by FPGA type

We’ve introduced the concepts behind triple modular redundancy (TMR) before, using built-in capability in Synopsys Synplify Premier to synthesize TMR circuitry into FPGAs automatically. A recent white paper authored by Angela Sutton revisits the subject… Read More

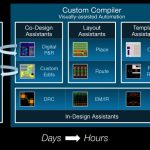

Custom IC Layout Design at #53DAC

Last week at the #53DAC conference there was a lot of excitement in the air about custom IC design, especially at the luncheon that I attended on Tuesday from Synopsys where they had customers like STMicroelectronics, GSI Technology, Samsung Foundry and the Synopsys IP group talk about their experiences using the new Custom Compiler… Read More

Webinar alert – another break in the memory wall

A couple months ago we heard from another vendor in a webinar on HBM and breaking through the “memory wall”. Next week Open Silicon weighs in on the topic in a webinar with partners SK Hynix and Synopsys.… Read More

ARM sets up quagmire-free ecosystem for IoT

Wandering around DAC this week, I found much of the discussion focused on the EDA community being at an inflection point. How do we get more design starts from new places with new ideas without jeopardizing existing business? It’s not as simple a transition as it sounds.… Read More