The growth of complexity for silicon test as it relates to test data volume and test times is driven by multiple concurrent factors. One dimension is simply the increase in silicon complexity. However, other factors are playing a role as well. These include higher reliability requirements for new applications such as automotive,… Read More

Tag: synopsys

Non Volatile Memory IP is Invaluable for PMICs

Power Management ICs are a vitally important part of system design. Evidence of this is cited by a Synopsys white paper that mentions how Apple acquired a portion of PMIC developer Dialog Semiconductor that was previously their exclusive PMIC supplier. Clearly Apple had decided that PMIC design was a strategic differentiating… Read More

The Intel Foundry Ecosystem Explained

Exciting times for the semiconductor industry! Last week Intel announced a billion dollar fund to build a foundry ecosystem and today Intel announced they are acquiring foundry Tower Semiconductor for $5.6 billion dollars, WOW! Some people doubted Intel’s commitment to the foundry market this time. I think we can now put that… Read More

The Semiconductor Ecosystem Explained

The last year has seen a ton written about the semiconductor industry: chip shortages, the CHIPS Act, our dependence on Taiwan and TSMC, China, etc.

But despite all this talk about chips and semiconductors, few understand how the industry is structured. I’ve found the best way to understand something complicated is to diagram… Read More

Why It’s Critical to Design in Security Early to Protect Automotive Systems from Hackers

Remember when a pair of ethical hackers remotely took over a Jeep Cherokee as it was being driven on a highway near downtown St. Louis back in 2015? The back story is, those “hackers,” security researchers Charlie Miller and Chris Valasek, approached vehicle manufacturers several years before their high-profile feat, warning… Read More

Upcoming Webinar: 3DIC Design from Concept to Silicon

Multi-die design is not a new concept. It has been around for a long time and has evolved from 2D level integration on to 2.5D and then to full 3D level implementations. Multiple driving forces have led to this progression. Whether the forces are driven by market needs, product needs, manufacturing technology availability or EDA… Read More

Identity and Data Encryption for PCIe and CXL Security

Privacy and security have always been a concern when it comes to computing. In prior decades for most people this meant protecting passwords and locking your computer. However, today more and more users are storing sensitive data in the cloud, where it needs to be protected at rest and while in motion. In a Synopsys webinar Dana Neustadter,… Read More

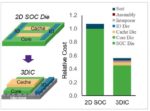

Heterogeneous Integration – A Cost Analysis

Heterogeneous integration (HI) is a general term used to represent the diverse possibilities for die technology incorporated into advanced 2.5D/3D packaging. At the recent International Electron Devices Meeting (IEDM) in San Francisco, a team from Synopsys and IC Knowledge presented data from analyses of future potential… Read More

Delivering Systemic Innovation to Power the Era of SysMoore

With the slowing down of Moore’s law , the industry as a whole has been working on various ways to maintain the rate of growth and advancements. A lot has been written up about various solutions being pursued to address specific aspects. The current era is being referred to by different names, SysMoore being one that Synopsys uses.… Read More

Is Ansys Reviving the Collaborative Business Model in EDA?

The Electronic Design Automation (EDA) industry used to be a bustling bazaar of scrappy startups, along with medium sized companies that dominated a technology space, and big main-line vendors. The annual Design Automation Conference was noisy, hectic, and sprawled over multiple large convention halls. This diversity meant… Read More