Today Atrenta and Mentor announced that they were collaborating to enable accurate, signoff quality power estimation at the RTL for entire SoCs. The idea is to facilitate RTL power estimation for designs of over 50M gates running actual software loads over hundreds of millions of cycles, resulting in simulation datasets in the… Read More

Tag: spyglass

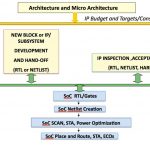

RTL Signoff Theater

We have talked for years about RTL signoff, the idea that a design could be finalized at the RTL level and then most of the signoff would take place there. Then the design would be passed to a physical implementation team who would not expect to run into any problems (such as routing congestion, missing the power budget or similar problems).… Read More

Atrenta at DAC…SpyGlass is Everywhere

Atrenta are at booth 1847 in the exhibit hall where there will be regular presentations in the “RTL Signoff Theater” and lots of presentations on various aspects of SpyGlass, GenSys and BugScope in their suites. The registration page for the suite sessions is here. Just who is presenting in the RTL Signoff Theater … Read More

SoC Derivatives Made Easier

Almost no design these days is created from scratch. Typical designs can contain 500 or more IP blocks. But there is still a big difference between the first design for a new system or platform, and later designs which can be extensively based on the old design. These are known as derivatives and should be much easier to design since… Read More

Global Design Closure

Satish Soman, chief solutions architect at Atrenta, was invited to give a presentation on Global Design Closure at the VLSI India conference in Pune at the start of this month. He talked about the need to close the gap between the typical SoC development methodology and what happens in reality.

SoCs are really put together in two … Read More

Are you good at identifying languages? Win an iPad Mini

Did you watch Atrenta’s holiday video (it’s only one minute)? Various Atrenta employees from all over the world wished you happy holidays in their own languages. Now Atrenta are having a competition. If you identify all the languages in the video then you can win an iPad Mini.

To enter the competition, or to view the … Read More

EDS Fair: Dateline Yohohama

Electronic Design and Solutions Fair (EDSF) was held in Yokohama Japan from Wednesday to Friday last week. It was held at the Pacifico Hotel, somewhere I have stayed several times, not far from the Yokohama branch of Hard Rock Cafe and, what used to be at least, the biggest ferris-wheel in the world.

Atrenta was one of the many companies… Read More

ARM adopting SpyGlass IP Kit, joining TSMC’s soft IP9000 Quality Assessment Program

More than one year old now, TSMC’s soft IP quality assessment program is a joint effort between TSMC and Atrenta to deploy a series of SpyGlass checks that create detailed reports of the completeness and robustness of soft IP. This soft IP quality program has been the first to be initiated by a Silicon foundry on other than “Hard IP”,… Read More

SpyGlass IP Kit 2.0

On Halloween, Atrenta and TSMC announced the availability of SpyGlass IP Kit 2.0. IP Kit is a fundamental element of TSMC’s soft IP9000 Quality Assessment program that assesses the robustness and completeness of soft (synthesizable) IP.

IP Kit 2.0 will be fully supported on TSMC-Online and available to all TSMC’s soft IP alliance… Read More

Atrenta Wins Gold

What is the most read article on design on EE Times website? Brian Bailey has an article up running through the top 10. It turns out that the #1 article is Understanding Clock Domain Issues by Saurabh Verma and Ashima S. Dabare of Atrenta. It actually had more than double the views of the second place paper. Checking clock domain crossing… Read More