Last May, Atrenta and TSMC announced the Soft-IP Alliance Program which uses SpyGlass and a subset of its GuideWare reference methodology to implement TSMC’s IP quality assessment program. TSMC requires all soft-IP providers to reach a minimum level of completeness before their IP is listed on TSMC online. Since TSMC … Read More

Tag: spyglass

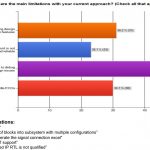

Atrenta’s users. Survey says….

Atrenta did an online survey of their users. Of course Atrenta’s users are not necessarily completely representative of the whole marketplace so it is unclear how the results would generalize for the bigger picture, your mileage may vary. About half the people were design engineers, a quarter CAD engineers and the rest … Read More

SoC Realization: Let’s Get Physical!

If you ask design groups what the biggest challenges are to getting a chip out on time, then the top two are usually verification, and getting closure after physical design. Not just timing closure, but power and area. One of the big drivers of this is predicting and avoiding excessive routing congestion, which is something that … Read More

Clock Domain Crossing (CDC) Verification

Multiple, independent clocks are quintessential in SoCs and other complex ASICs today. In some cases, such as in large communications processors, clock domains may number in the hundreds. Clock domain crossings pose a growing challenge to chip designers, and constitute a major source of design errors–errors that can… Read More