About 35 years ago the first commercial SPICE circuit simulators emerged and they were quickly put to work helping circuit designers predict the timing and power of 6um NMOS designs. Then we had to limit our circuit simulations to just hundreds of transistors and interconnect elements to fit into the RAM and complete simulation… Read More

Tag: spice

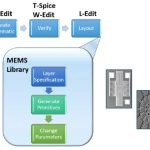

Mass customization coming to MEMS?

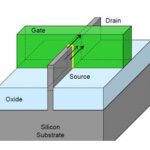

With the industry abuzz about the Apple purchase of a Maxim Integrated fab as a potential R&D facility for MEMS design, it begs the question: is creating a MEMS device that easy?

MEMS technology is approaching the same fork in the road where digital design encountered LSI four decades earlier. … Read More

All Models Are Wrong, Some Are Useful

“All models are wrong, some are useful.” This remark is attributed to the statistician George Box who used it as the section heading in a paper published in 1976.

Just for fun I looked up a few semiconductor statistics from 1976. Total capital spending was $238M in Japan and $306M in US and…that’s it, there was nobody else back then … Read More

Replacing the British Museum Algorithm

In principle, one way to address variation is to do simulations at lots of PVT corners. In practice, most of this simulation is wasted since it adds no new information, and even so, important corners will get missed. This is what Sifuei Ku of Microsemi calls the British Museum Algorithm. You walk everywhere. And if you don’t walk to… Read More

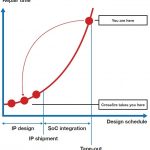

Foolproof Your IP before it Stumbles in Higher-up Design

SoC designs are increasingly becoming assemblies of a large number of IP blocks. A well integrated assembly can lead to a successful PPA (Power, Performance and Area) optimized design. However, it is equally important that each IP block is optimized, robust, and integrable in the design. The complexity of an IP and its integration… Read More

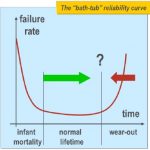

Predicting Lifetime of Analog ICs

With the increase of transistors per unit area, high density interconnects and manufacturing variability at lower nodes, the electronic devices have become more vulnerable to failures. The devices that operate under extreme conditions such as automotive devices that operate at high temperatures need to be robust enough to… Read More

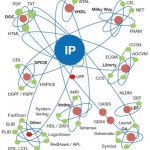

An Universe of Formats for IP Validation

Although I knew about Crossfire’s capabilities for signing off quality of an IP before its integration into an SoC, there was much more to learn about this tool when I visited Fractal Technologies booth during this DAC. The complexity handled by this tool to qualify any type of IP for its integration into an SoC can be imagined by the… Read More

Eyes Meet Innovations at DAC

It gives me a very nice, somewhat nostalgic, feeling after attending the 52[SUP]nd[/SUP] DAC. There was a period during my final academic year in 1990 and my first job when I used to search through good technical papers in DAC proceedings and try implementing those concepts in my project work. In general, representation from ‘R&D… Read More

Making Things Visible for 25 Years

This year is most notably the 50th anniversary of Moore’s Law. It is also the 25th anniversary of Concept Engineering. They were founded in 1990 in Freiburg Germany. They started by providing automatic schematic generation from netlist. They sold primarily to other EDA companies and to internal development groups in semiconductor… Read More

Starvision Pro: Lattice Semiconductor’s Experience

During SNUG I took the opportunity to chat to Choon-Hoe Yeoh of Lattice Semiconductor about how they use Concept Engineering’s Starvision Pro product. He is the senior director of EDA tools and methodologies there.

Lattice Semiconductor is a manufacturer of low-power, small-footprint, low-cost programmable logic devices.… Read More