FPGAs have become a lot more capable and a lot more powerful, more closely resembling SoCs than the glue-logic we once considered them to be. Look at any big FPGA – a Xilinx Zynq, an Intel/Altera Arria or a Microsemi SmartFusion; these devices are full-blown SoCs, functionally different from an ASIC SoC only in that some of the device… Read More

Tag: soc

CEO Interview: Sanjay Keswani of Consensia

Sanjay Keswani founded Consensia in 2013. He has deep experience in the high-tech industry, guiding some of the world’s high profile technology brands through complex innovation and business transformation projects including companies such as Atmel, KLA-Tencor, Hughes Aircraft, and Motorola Mobility. Consensia customers… Read More

Unlocking Access to SOC’s for IoT Edge Product Developers

In the wake of the many mega mergers and consolidation in the semiconductor and electronics space, it is easy to say that opportunities for smaller companies are shrinking. Indeed, quite the opposite might be true. The larger companies, like Broadcom, ARM, Qualcomm, Analog Devices, Microchip, Maxim and Infineon (to name a few)… Read More

Improved Timing Closure for Network-on-Chip based SOC’s

Network on chip (NoC) already has a long list of compelling reasons driving its use in large SOC designs. However, this week Arteris introduced their PIANO 2.0 software that provides an even more compelling reason to use their FlexNoC architecture. Let’s recap. Arteris FlexNoC gives SOC architects and designers a powerful tool… Read More

Four Barriers to Using an SoC for IoT Projects

I often read about the large number of expected IoT design starts around the world, so I started to think about what the barriers are for launching this industry in order to meet the projections. One of my favorite IoT devices is the Garmin Edge 820, a computer for cyclists that has sensors for speed, cadence, power, heart rate, altitude… Read More

Aldec Rounds Out ALINT-PRO Checker

If there’s anyone out there who still doesn’t accept the importance of static RTL verification in the arsenal of functional verification methods, I haven’t met any recently. That wasn’t the case in my early days in this field. Back then I grew used to hearing “I don’t make mistakes in my RTL”, “I’ll catch that in simulation”, “My editor… Read More

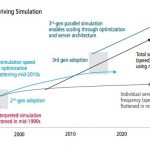

Making Functional Simulation Faster with a Parallel Approach

I’ll never forgot working at Intel on a team designing a graphics chip when we wanted to simulate to ensure proper functionality before tapeout, however because of the long run times it was decided to make a compromise to speed things up by reducing the size of the display window to just 32×32 pixels. Well, when first silicon… Read More

SoC Integration using IP Lifecycle Management Methodology

Small EDA companies often focus on a single point tool and then gradually over time they add new, complementary tools to start creating more of a sub-flow to help you get that next SoC project out on time. The most astute EDA companies often choose to partner with other like-minded companies to create tools that work together well,… Read More

Timing Closure Complexity Mounts at FinFET Nodes

Timing closure is the perennial issue in digital IC design. While the specific problem that has needed to be solved to achieve timing closure over the decades has continuously changed, it has always been a looming problem. And the timing closure problem has gotten more severe with 16/14nm FinFET SoCs due to greater distances between… Read More

Fan-Out Wafer Level Processing Gets Boost from Mentor TSMC Collaboration

I caught up with John Ferguson of Mentor Graphics this week to learn more about a recent announcement that TSMC has extended its collaboration with Mentor in the area of Fan-Out Wafer Level Processing (FOWLP).

In March of last year Mentor and TSMC announced that they were collaborating on a design and verification flow for TSMC’s… Read More