As the semiconductor design community is seeing higher and higher levels of abstraction with standard IPs and other complex, customized IPs and sub-systems integrated together at the system level, sooner than later we will find SoCs to be just assemblies of numerous IPs selected off-the-self according to the design needs and… Read More

Tag: soc

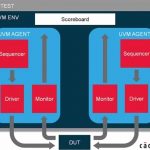

So Easy To Learn VIP Integration into UVM Environment

It goes without saying that VIPs really play a Very Important Part in SoC verification today. It has created a significant semiconductor market segment in the fabless world of SoC and IP design & verification. In order to meet the aggressive time-to-market for IPs and SoCs, it’s imperative that readymade VIPs which are proven… Read More

TSMC (TSM) is Having Another SoC Year!

TSMC’s stock has more than doubled in the last five years. Coincidentally that is when I started blogging about TSMC. QCOM stock has experienced a similar doubling during this time as have other TSMC customers. The question is: What is next for TSMC? As I have mentioned before, you would be better off taking stock tips from your dog… Read More

Synopsys Galaxy Platform & Lynx Design System supports FD-SOI

This is a new brick that Synopsys brings to build FD-SOI credibility. We have talked at Semiwiki about FD-SOI technology developed by the LETI and STM, and recently endorsed by Samsung Foundry, offering a more than credible second source to STM. And we have said that the FD-SOI introduction will need to be supported by EDA and IP vendors… Read More

Different Approaches to System Level Power Modeling and Analysis for Early Design Phases

At DATEthis year in Dresden, Bernhard Fischer from Siemens CT(Corporate Technology) has presented an interesting summary of the various techniques used for power modeling and analysis at the architectural level. He went through the pros and cons of using spreadsheets, timed virtual platforms annotated with power numbers … Read More

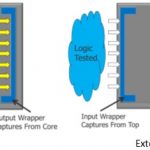

Taming The Challenges of SoC Testability

With the advent of large SoCs in semiconductor design space, verification of SoCs has become extremely challenging; no single approach works. And when the size of an SoC can grow to billions of gates, the traditional methods of testability of chips may no longer remain viable considering the needs of large ATPG, memory footprint,… Read More

LSI’s Way of Faster & Reliable Electronic System Design

LSI Corporationstarted in 1980s and I had several encounters with it during my jobs in 1990s; not to forget the LSI chips I used to see in desktops and other electronic systems, and I’m happy to see LSI continuing today with more vigour having leadership position in storage and networking space. It provides highly reliable, high … Read More

System Design: Turtles All the Way Down

According to Steven Hawking, Bertrand Russell once gave a public lecture on astronomy. He described how the earth orbits around the sun and how the sun orbits around our galaxy. At the end of the lecture, a little old lady at the back of the room got up and said: “What you have told us is rubbish. The world is really a flat plate supported… Read More

Importance of Data Management in SoC Verification

In an era of SoCs with millions of gates, hundreds of IPs and multiple ways to verify designs through several stages of transformations at different levels of hierarchies, it is increasingly difficult to handle such large data in a consistent and efficient way. The hardware and software, and their interactions, have to be consistent… Read More

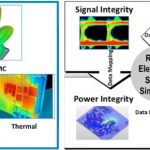

Power and Thermal Simulation in ESL Verification Flows

At the recent DVcon there was a keen focus on design verification and validation. Much of the attention is on Logic/circuit design verification, UVM, and IP verification. At the system level functional verification has improved to comprehend complex hardware and software interaction using Virtual Platforms/SystemC and Transaction… Read More