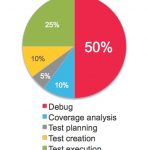

Sure, design engineers can get more attention than verification engineers, but the greater number of verification engineers on SoC projects means that the verification task is a bigger bottleneck in a schedule than pure design work. A recent survey conducted at Cadence shows how verification effort can be divided into several,… Read More

Tag: soc

Rockchip Bets on Arteris FlexNoC Interconnect IP to Leapfrog SoC Design

China was a virgin territory for Arteris Inc. before July 19, 2012 when Fuzhou Rockchip Electronics announced that it has licensed the Arteris FlexNoC network-on-chip (NoC)-based interconnect IP technology for its multicore SoCs for budget Android tablets. Rockchip mostly targets the tablet and set-top box (STB) markets … Read More

Successful Venture of an Indian Global VIP Company

It’s rare that we find a truly Indian-based company operating globally in the semiconductor space. Although the ‘gold rush’ towards IP development in the last decade initiated many IP start-ups in India, today we rarely find Indian IP company names which are shining in the global arena. The story of services companies is different,… Read More

Security All Around in SoCs at DAC

Last month I was on my way to write a detailed article on important aspects to look at while designing an SoC. This was important in the new context of modern SoCs that go much beyond the traditional power, performance and area (PPA) requirements. I had about 12-13 parameters in my list that I couldn’t cover in one go, so I put the write-up… Read More

The Earth is Not Flat; Neither is IP

Chip design is largely about assembling pre-designed IP, either developed in other groups in the same company, or brought in from a 3rd party, or occasionally developed within the SoC design group itself. But that makes it sound like it is a bunch of blocks linked together with some interconnect, but of course another important … Read More

Medicals Marriage with Semis

I remember a couple of decades ago, my father used to go to a nearby doctor’s clinic to get his blood pressure and sugar levels checked. I guess, in around 1990s small electronic kits became available to measure these usual daily health indicators and instantly display the numbers. I bought a few for my father then. Today, the scene… Read More

Apple’s ARMed History

Apple has redefined three industries within a decade: media player with the iPod, mobile handset with the iPhone and portable computers with the iPad. If there is anything common in these three game-changing product development stories other than Apple, it’s the ARM footprint. Even now the technology media is abuzz with speculation… Read More

SoCs in New Context Look beyond PPA

If we look back in the last century, performance and area were two main criteria for semiconductor chip design. All design tools and flows were concentrated towards optimizing those two aspects. As a result, density of chips started increasing and power became a critical factor. Now, Power, Performance and Area (PPA) are looked… Read More

CDC Verification: A Must for IP and SoCs

In the modern SoC era, verification is no longer a post-design activity. The verification strategy must be planned much earlier in the design cycle; otherwise the verification closure can become a never ending problem. Moreover, verification which appears to be complete may actually be incomplete because of undetected issues… Read More

Getting a Grip on the Internet of Things

QuickLogic’s CTO Tim Saxe gave a keynote Getting a Grip on the Internet of Things at the IoT Summit last week.

He started by relating how things have changed over the last 3 years when he talks to customers.

- Three years ago it was sensor hubs in smartphones and the power budget was 3mW (so one day between re-charging, something