A week ago I was reading an article written by Daniel Nenni where he emphasised about semiconductor acquisitions to fuel innovation. We would see that in a larger space, not only in semiconductor and FPGA manufacturing companies (e.g. Intel and Altera) but also in the whole semiconductor ecosystem. If we see it from technical perspective,… Read More

Tag: soc

Logic Synthesis Reborn

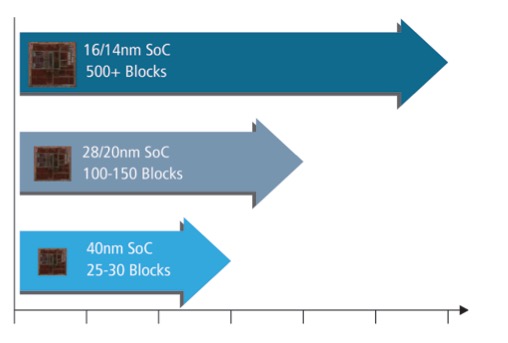

Combine the pressures of Moore’s Law which enable billion transistor SoCs and the shortened time to market from consumer electronics product cycles and you have the perfect storm for EDA tool vendors. A modern SoC can have 500 or more blocks, creating both a design and verification challenge. How in the world do you write … Read More

A Robust Lint Methodology Ensures Faster Design Closure

With the increase in SoC designs’ sizes and complexities, the verification continuum has grown larger to an extent that the strategies for design convergence need to be applied from the very beginning of the design flow. Often designers are stuck with never ending iterations between RTL, gate and transistor levels at different… Read More

A Key Partner in the Semiconductor Ecosystem

Often we hear about isolated instances of excellence from various companies in the semiconductor industry which contribute significantly in building the overall ecosystem. While the individual excellence is essential, it’s rather more important how that excellence is utilized in a larger way by the industry to create a ‘value… Read More

Design Collaboration, Requirements and IP Management at #52DAC

For SoC designers attending DAC in June you probably want to check out the EDA vendors that enable design collaboration among your engineers and designers that are spread out across a building, campus or the globe. Dassault Systemes does offer tools and methodologies for: Design collaboration, requirements and IP management.… Read More

Quark Adds Muscle to Intel in the IoT World

We have been hearing about Intel’s Quark processor, which is based on its good old Pentium, making waves in IoT world. The CPU core of Quark is said to be the smallest in Intel. It is supposed to be inexpensive and extremely low in power; a perfect combination for IoT devices. The Pentium architecture equips the processor to perform… Read More

Saving Time and Money on Your Next SoC Project

Every SoC project that I know of wants to finish on time, under budget, and maximize profits per device. When I first started out doing DRAM design I learned that we could maximize profit by doing shrinks of existing designs, move from ceramic to plastic packages, and reduce the amount of time spent on a tester. Today, the economic … Read More

Experts Talk at Mentor Booth

It’s less than four weeks to go at DAC 2015 and the program is final now. So I started investigating new technologies, trends, methodologies, and tools that will be unveiled and discussed in this DAC. In the hindsight of the semiconductor industry over the last year, I see 14nm technologies in the realization stage and 10nm beckoning… Read More

SoCs in New Context Look beyond PPA – Part2

In the first part of this article, I talked about some of the key business aspects along with some technical aspects like system performance, functionality, and IP integration that drive the architecture of an SoC for its best optimization and realization in an economic sense. In this part, let’s dive into some more aspects that… Read More

SoC’s Shift Left Needs Software Integrity

Since Aart de Geus, co-CEO and co-founder of Synopsys, gave his keynote at the Synopsys User Group (SNUG) conference in Silicon Valley last March, I’ve been hearing a lot more about the “Shift Left” in semiconductor design. Although I couldn’t attend Synopsys’ 25[SUP]th[/SUP]SNUG, I found some short videos on the Synopsys website… Read More