You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Before this DAC I had never even heard of ICScape, so on Monday and Wednesday I visited their booth to find out their story.

Steve Yang, Ph.D. (Co-founder and President), Ravi Ravikumar (Marketing)

ICScape was founded in 2005 in Santa Clara by Steve Yang (Circuit Design engineer for microprocessor, Synopsys) and Jason Xing (Sun… Read More

Britto Vincent of ProPlus Design Solutions met with me at DAC on Monday morning to talk about Design For Yield (DFY) and Analog Fast SPICE.

In 2011 ProPlus announced DFY tools where the technology came from IBM, it provides fast Monte Carlo results up to 3 sigma, then added NanoSpice for faster simulation results. Similar in approach… Read More

Partitioning Panelby Paul McLellan on 06-06-2012 at 4:53 pmCategories: EDA, Events

I moderated a panel on partitioning today and I have to say that I learned some things. The panelists were Jonathan DeMent from IBM, Santosh Santosh from NVIDIA and Hao Nham of eSilicon. Considering the different types of designs being done their approach to partitioning and the reasons for doing so were very similar.

When you first… Read More

Wednesday morning I attended a panel discussion with: ARM, IBM, Cadence, GLOBALFOUNDRIES and Samsung.

The panelists all sang the same song of collaboration between EDA, IP and Foundry to enable 28nm, 20nm and even 14nm.… Read More

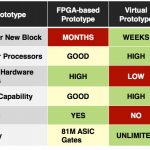

There are two main approaches to building a substructure on which to do software development and architectural analysis before a chip is ready: virtual platforms and FPGA prototyping.

Virtual platforms have the advantage that they are fairly quick to produce and can be created a long time before RTL design for the various blocks… Read More

On Wednesday there is a User Track Poster Session that examines the design impact of process variation in GLOBALFOUNDRIES 28nm technology. For those of you who are wondering what process variation looks like at 20nm take this 28nm example and multiply it by one hundred (slight exaggeration, maybe).

Variation effects have a significant… Read More

Spyglass by Atrentaby Paul McLellan on 06-03-2012 at 4:27 pmCategories: EDA

I’ve been helping get booths set up at DAC in Moscone for the last couple of days. Atrenta’s booth shows their new branding that I talked about last week. Now you can see what they are doing in this picture of their booth. As I sort of guessed they are leading with the Spyglass name. The booth says everywhere “Spyglass… Read More

This evening at Silicon Valley Bank was the first of what is planned to be a series about EDA startups. Apparently the seed of the idea was planted by Dan Nenni with Jim Hogan and Steve Pollock and the EDAC Emerging Companies committee ran with it.… Read More

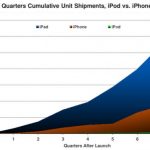

Every year or so Mary Meeker (at Kleiner-Perkins) does a big presentation on internet trends. Since the internet in general and mobile in particular is a big driver for the semiconductor industry, this report is a treasure trove of useful data and interesting facts.

For example, this graph shows the adoption rate of iPods, iPhones… Read More

SpyGlass…the Mysteryby Paul McLellan on 05-30-2012 at 1:30 amCategories: EDA

Atrenta have put out a mysterious press release, a sort of teaser for what they are up to at DAC.

The first part is that they have an interview program at their booth (#2230) on the show floor where customers, partners and investors will talk about SpyGlass. Current speakers are:

- Jack Browne (Sonics)

- Jim Hogan (private investor)

- Charlie

…

Read More