Low power is the hottest topic these days. The designers of hardware and software are trying to find instances where they can save power . This article tries to identify the role that can be played by the hardware which traditionally it is always software who drives it.… Read More

Tag: semiconductor

Wiring Harness Design

In 2003 Mentor acquired a company doing wiring harness design. Being a semiconductor guy this wasn’t an area I’d had much to do with. But more than most semiconductor people I expect.

But back when I was an undergraduate, I had worked as a programmer for a subsidiary of Philips called Unicam that made a huge range of spectrometers… Read More

A Brief History of Semiconductors: the Foundry Transition

A modern fab can cost as much as $10B dollars. That’s billion with a B. Since it has a lifetime of perhaps 5 years, owning a fab costs around $50 per second and that’s before you buy any silicon or chemicals or design any chips. Obviously anyone owning a fab had better be planning on making and selling a lot of chips if they are going to make… Read More

3D Memories

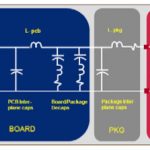

At DesignCon earlier this year, Tim Hollis of Micron gave an interesting presentation on 3D memories. For sure the first applications of true 3D chips are going to be stacks of memory die and memory on logic. The gains from high bandwidth access to the memory and the physically closer distance from memory to processor are huge.

Micron… Read More

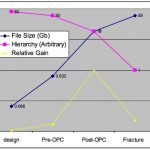

The Need for OASIS in Post-layout IC Databases

OASIS is a hierarchical IC file format used for IC designs that is gradually replacing GDS II throughout the mask data stages. The compelling reason for using OASIS has always been the reduction of file size, and speed up of processing times through the use of hierarchy and fewer translation steps.

At the 45nm node an actual M1 layer… Read More

TSMC 28nm Update Q3 2012!

Reports out of Taiwan (I’m in Hsinchu this week) have TSMC more than doubling 28nm wafer output in Q3 2012 due to yield improvements and capacity increases while only spending $3.6B of the $8.5B forecasted CAPEX! Current estimates have TSMC 28nm capacity at 100,000 300mm wafers (+/- 10%) per month versus 25,000 wafers reported… Read More

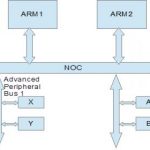

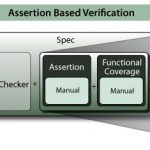

Assertion Synthesis

In June, Atrenta acquired NextOp, the leader in assertion synthesis. So what is it?

Depending on who you ask, verification is a huge fraction, 60-80%, of the cost of an SoC design, so obviously any technology that can reduce the cost of verification has a major impact on the overall cost and schedule of a design. At a high-level, verification… Read More

Power, Signal, Thermal and EMI signoff

Increasingly the challenge with SoCs, especially for mobile, is not getting the performance high enough but doing so in a power-efficient manner. Handheld devices running multiple apps need high-speed processors that consume extremely low levels of power both in operating and standby modes. In the server farm, the limit is … Read More

Apple’s Victory Will Re-Shuffle the Semi Industry

Apple’s legal victory over Samsung has been analyzed in thousands of articles and TWEETs since last Friday’s announcement and surely more will follow. Most of the commentary has focused on the first order impact to handset manufacturers. It is not entirely clear how it will all settle but there are sure to be secondary ramifications… Read More

A Brief History of ASIC, part II

All semiconductor companies were caught up in ASIC in some way or another because of the basic economics. Semiconductor technology allowed medium sized designs to be done, and medium sized designs were pretty much all different. The technology didn’t yet allow whole systems to be put on a single chip. So semiconductor companies… Read More