When I started in this business, we were at 3 micron HMOS. A few other things are close to that size. A red blood cells is about 9 microns, a human hair is about 100 microns. And in a bizarre “only in Japan” video, people compete to plane the thinnest shaving off a plank of wood. It turns out the answer is 9 microns. That’s… Read More

Tag: semiconductor

Apple and Samsung Do It Again

The numbers are starting to come in for how everyone did in Q4. According to Cannacord Genuity, Apple made 69% of the profit and Samsung made 34%. What do you notice about those numbers? They add up to more than 100%. HTC supposedly made 1% of the profit and everyone else either broke even or lost money. Basically Apple and Samsung have… Read More

Tubes of the Future

So what is a silicon nanowire? It is basically a FET where the active element is a wire 3-20nm in diameter. So where a FinFET has the gate wrapped around 3 sides of the transistor, a nanowire (NW) has it wrapped around all four. In essence, the wire runs through the middle of the gate.

There seem to be three issues about building a silicon… Read More

ARMs in the Clouds

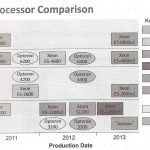

The most interesting session at the Linley Tech Data Center Conference last week was the last one, on Designing Power Efficient Servers. What this was really about was whether ARM would have any success in the server market and what Intel’s response might be.

Datacenters are now very focused on power efficiency and many track… Read More

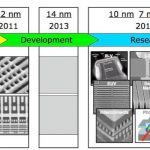

No EUV before 7nm?

I was at the Common Platform Technology Forum this week. One of the most interesting sessions is IBM’s Gary Patton giving an overview of the state of semiconductor fabrication. Then, at lunchtime, he is one of the people that the press can question. In this post, I’m going to focus on Extreme Ultra-Violet (EUV) lithography.… Read More

Sanjiv Kaul is New CEO of Calypto

Calypto announced that Sanjiv Kaul is the new CEO. I first met Sanjiv many years ago when he was still at Synopsys when I interviewed for a position there around the time I transitioned out of Compass and went back to the parent company VLSI. I forget what the position was. Then about three or four years ago when I did some work for Oasys… Read More

Software Driven Power Analysis

Power is a fundamentally hard problem. When you have finished the design, you have accurate power numbers but can’t do anything about them. At the RTL level you have some power information but it is often too late to make major architectural changes (add an offload audio-processor, for example). Early in the design, making… Read More

Startups: the Biggest Challenge

What is the biggest challenge facing an EDA startup today? By a startup, I mean a brand new company, not a company that already has a few customers and is either on a fast path to success or a slower path whereby the company can continue to grow slowly forever.

Obviously, one challenge is the funding environment. Since EDA acquisitions… Read More

TSMC ♥ Oasys

Oasys has joined the TSMC Soft-IP Alliance Program. This means that TSMC IP partners have access to a new RTL exploration tool to improve QoR and reduce the iterations needed for design closure. In modern process nodes, RTL engineers implementing complex IP cores for graphics, networking, and mobile computing are struggling … Read More

Going to DAC 2013 in Austin? The Country’s Best Barbecue is a 20 Minute Walk

Going to DAC? I just booked my plane ticket last weekend since flights from the Bay Area to wherever DAC is are so often overbooked. It’s in Austin this year in case you’ve been living under a rock. There are lots of reasons to go, from the academic conference to the world’s biggest EDA exhibition. And here is one … Read More