As Moore’s law started saturating on a single semiconductor die, the semiconductor community came up with the approach of growing vertically by stacking dies one above other in a 3D-IC arrangement. However, a major concern with a 3D-IC is that the heat generated by each die can get trapped in the stack, and hence it’s extremely important… Read More

Tag: semiconductor

Advancements in Nanoscale Manufacturing

I’m at the GSA Silicon Summit today, at the computer history museum. The first panel session this morning was about future process technology. It was moderated by Joe Sawicki of Mentor with a panel consisting of Rob Aitken from ARM, Paul Farrar of G450C, Peter Huang of TSMC, John Kibarian of PDF Solutions and someone from Applied… Read More

Mentor’s New Enterprise Verification Platform

I spent the morning at Mentor where they announced their new enterprise verification platform. This was a general announcement but was attended by a lot of the international press who were over on a GlobalPress tour (the event that used to take up camp at Chaminade).

But first Wally Rhines spent 30 minutes giving a nice overview of… Read More

FD-SOI, FinFET, 3D in Monterey

Last night the IEEE Silicon Valley Chapter had a panel session that was in some ways a preview of some of what will be discussed at the Electronic Design Process Symposium in Monterey next Thursday and Friday. At EDPS Herb Reiter organized a session on FinFET, 3DIC and FD-SOI (sort of how many buzzwords can you get into one set of titles).… Read More

Sonics Performance Monitor and Hardware Trace

As SoCs have got more complex, and with a larger and larger software content, it is no longer good enough to just monitor how the design behaves using simulation and then completely forget about it once the design is complete. What is required is the capability to monitor the design in real time (in silicon or FPGA) to see how it is behaving.… Read More

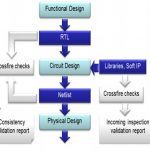

Semiconductor IP Validation Gets Faster

Semiconductor IP continues to grow in use for SoC design, and many chips can now use hundreds of IP blocks from multiple vendors. Validating the quality of the IP blocks is an important step in the design process, and you could perform manual validation and inspection of each new IP block at the expense of time and engineering effort.… Read More

EDAC Mixer: Sonoma Chicken Coop

Get together with your fellow industry peers and insiders at the monthly EDAC Mixer, to the benefit of local charities. You don’t need to donate anything, you just show up and pay for your own drinks. A portion of the proceeds will go to local charities, this month to the Resource Area for Teaching (RAFT), a San Jose based non-profit… Read More

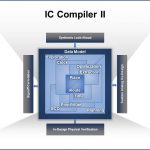

SNUG and IC Compiler II

I have been at SNUG for the last couple of days. The big announcement is IC Compiler II. It was a big part of Aart’s keynote and Monday lunch featured all the lead customers talking about their experience with the tool.

The big motivation for IC Compiler II was to create a fully multi-threaded physical design tool that will scale… Read More

Imagine what all the DLP technology can do for you

Light has become integral part of most of the electronic devices we use today in any sphere of influence; personal, entertainment, consumer, automotive, medical, security, and industrial and so on. It’s obvious; along with IoT (Internet-of-Things) devices, the devices to illuminate and display things will play a major role… Read More

IC Implementation Tool Gets a Rewrite, Now 10X Faster

EDA start-up companies often have the advantage over established vendors by being able to start from scratch, instead of having to maintain some legacy code that no longer is competitive. But what happens when the established vendor decides to rewrite their IC implementation tools from scratch? In this case it’s good news,… Read More