Oh, our semiconductor industry just loves acronyms, and the title of my blog packs three of the most popular acronyms together at once. I attended a webinar hosted by Aldec last week on this topic, “UVM Simulation-based environment for Ibex RISC-V CPU core with Google RISC-V DV“. Verification engineers have been … Read More

Tag: riviera-pro

Webinar: Fast-Track to Riviera-PRO

Whether you’re right out of college, starting on your first design, a burn-and-churn designer thinking there must be a better way or an ASIC designer wanting to do a little prototyping, this webinar may be for you. It’s a fast start on using the Aldec Riviera-PRO platform for verification setup, run and debug, and more. There are … Read More

Cloud-Based Emulation

At the risk of attracting contempt from terminology purists, I think most of us would agree that emulation is a great way to prototype a hardware design before you commit to building, especially when you need to test system software together with that prototype. But setting up your own emulation resource isn’t for everyone. The … Read More

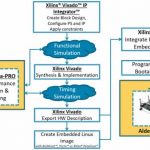

HW and SW Co-verification for Xilinx Zynq SoC FPGAs

It constantly amazes me at how much FGPA companies like Xilinx have done to bring ARM-based CPUs into a programmable SoC along with FPGA glue logic. Xilinx offers the Zynq 7000 and Zynq UltraScale+ SoCs to systems designers as a way to quickly get their ideas into the marketplace. A side effect of all this programability and flexibility… Read More

Aldec Swings for the Fences

In today’s fast-moving technology markets, companies who are prepared to step up to opportunity can break out of traditional bounds to become players in bigger and fast-growing markets. It looks to me like Aldec is putting itself on that path. They have announced an end-to-end hardware/software co-verification solution… Read More

Aldec Rounds Out ALINT-PRO Checker

If there’s anyone out there who still doesn’t accept the importance of static RTL verification in the arsenal of functional verification methods, I haven’t met any recently. That wasn’t the case in my early days in this field. Back then I grew used to hearing “I don’t make mistakes in my RTL”, “I’ll catch that in simulation”, “My editor… Read More

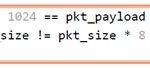

Optimization and verification wins in IoT designs

Designers tend to put tons of energy into pre-silicon verification of SoCs, with millions of dollars on the line if a piece of silicon fails due to a design flaw. Are programmable logic designers, particularly those working with an SoC such as the Xilinx Zynq, flirting with danger by not putting enough effort into verification?… Read More

Webinar alert – VHDL guru says its time to move up

Many years ago when I worked for Ed Staiano at Motorola, I learned never to use the word “comfortable” in a career context. I’m comfortable being with family and friends. This new high-back chair I sit in at my new faux-cocobolo desk (slightly distressed chalk-painted wood and industrial piping, awesome) is comfortable,… Read More

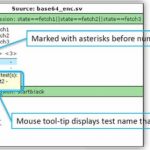

Design units come to faster Riviera-PRO release

For the latest incremental improvements to its Riviera-PRO functional verification platform, Aldec has turned to streamlining random constraint performance. The new Riviera-PRO 2016.02 release also is now fully supported on Windows 10 and adds a new debugger tool.… Read More

Aldec updates two EDA product lines

Continuous, incremental improvement based on customer feedback and insight from researchers is a pillar of the Aldec EDA strategy. Within the last two weeks, two of the Aldec product lines – Riviera-PRO, and ALINT-PRO-CDC – have seen new version releases. Here’s a quick look at some of the highlights of both.

Riviera-PRO 2015.06… Read More