Dan is joined by Charlie Cheng, Managing Director of Polyhedron. Prior to that, Charlie was the CEO of Kilopass Technology, where he grew the core memory business into a successful acquisition by Synopsys. Before that, Charlie was an Entrepreneur in Residence at US Venture Partners and a Corporate VP at Faraday Technology, a Taiwanese… Read More

RISC-V is a general-purpose license-free open Instruction Set Architecture [ISA] with multiple extensions. It is an ISA separated into a small base integer ISA, usable as a base for customized accelerators and optional standard extensions to support general-purpose software development. RISC-V supports both 32-bit and … Read More

The wearables electronics market is a large and fast growing one. According to Precedence Research, the global wearable technology market is expected to grow at a compound annual growth rate of 13.89% during the forecast period 2022 to 2030. Precedence estimated the global wearable technology market size at USD 121.7 billion… Read More

How do you reconfigure system characteristics? The answer to that question is well established – through software. Make the underlying hardware general enough and use platform software to update behaviors and tweak hardware configuration registers. This simple fact drove the explosion of embedded processors everywhere … Read More

I am delighted to share my technical insights into RISC-V in this article to inspire and prepare the next generation of chip designers for the future of the open era of computing. If you understand how we build complex electronic devices like desktops and smartphones using processors, you would be more interested in learning and… Read More

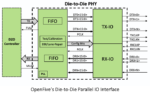

SemiWiki has been tracking the popularity of chiplets for two years now so it was not surprising to see that they played a key role at DAC. The other trend we foresaw was that the ASIC companies would be early chiplet adopters and that has proven true. One of the more vocal proponents of chiplets at DAC#59 was OpenFive, a 17+ year spec-to-silicon… Read More

In cybersecurity circles, the elephant in the room is a quantum computer in the hands of nefarious actors. A day is coming, soon, when well-funded organizations will be able to rent time on, or maybe even build or buy a quantum machine. Then, if data is valuable enough, people will hunt for it. Two or three months of compute time on a … Read More

Monday at DAC I was able to meet with Dr. Ashish Darbari, the CEO and founder of Axiomise. Ashish had a busy DAC, appearing as a panelist at, “Those Darn Bugs! When Will They be Exterminated for Good?”; and then presenting, “Taming the Beast: RISC-V Formal Verification Made Easy.”

I had read a bit about Axiomise… Read More

When more than one person is working on any project, coordination is imperative. When the team size grows, being in sync becomes essential. When it comes to SoC design management, registers and bit fields are used to communicate status of results and execute conditional controls. The Register Management function plays an essential… Read More

Recently, in one of my regular check-ins with AMIQ EDA, I was pleased that they linked me up with an active customer. The resulting post summarized my discussion with three engineers from Kepler Communications Inc. They talked about using one of the AMIQ EDA products in the design of FPGAs for space-borne Internet connectivity.… Read More