You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

As power integrity challenges increase with advanced nodes and multi-die architectures, EMIR analysis must evolve beyond traditional signoff. In this Synopsys webinar, we will show how RedHawk-SC is expanding its capabilities not only to enhance EMIR analysis, but also to enable IR-aware Static Timing Analysis (IR-STA) … Read More

As semiconductors continue to scale, designers are turning to 3DIC architectures to meet increasing demands for performance, energy efficiency, and functional density in data centers and edge AI applications. However, stacking multiple dies introduces new multiphysics challenges including electrical, structural, and… Read More

The electronic design community is well aware that it faces a daunting challenge to analyze and sign off the next generation of huge multi-die 3D-IC systems. Most of today’s EDA tools require extraordinary resources in specialized computers with terabytes of RAM and hundreds of processors. Customers don’t want to keep buying… Read More

On the eve of the Innovative Designs Enabled by Ansys Semiconductor (IDEAS) Forum I spoke with Vic on a range of topics including his opening keynote: Accelerating Moore and Beyond Moore with Multiphysics. You can register here.

Vic Kulkarni is Vice President and Chief Strategist, Semiconductor Business Unit, Ansys, San Jose.… Read More

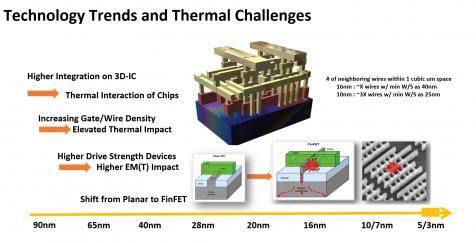

Advanced IC technologies, 5nm and 7nm FinFET design and stacked packaging, are enabling massive levels of integration of super-fast circuits. These in turn enable much of the exciting new technology we hear so much about: mobile gaming and ultra-high definition mobile video through enhanced mobile broadband in 5G, which requires… Read More

Designing with advanced-nodes FinFETs such as 7nm node involves a more complex process than prior nodes. As secondary physical effects are no longer negligible, the traditional margin-based approach applied at various design abstraction levels is considered ineffective. Coupled with the increase of device counts, failing… Read More

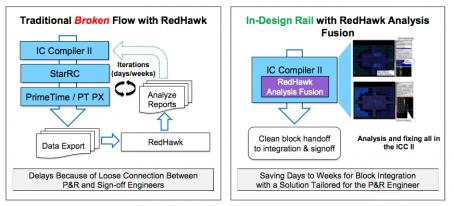

There’s a familiar saying that you can’t improve what you can’t measure. Taking that one step further, the more improvement you want, the more accurately you have to measure. This become pretty important when you’re building huge designs in advanced technologies. Margins are a lot tighter all round and use-cases are massively… Read More

There is a nice serendipity in discovering that two companies I cover are working together. Good for them naturally but makes my job easier because I already have a good idea about the benefits of the partnership. Synopsys and ANSYS announced a collaboration at DAC 2017 for accelerating design optimization for HPS, mobile and automotive.… Read More

I’m not going to be at DAC this year because I scheduled a fishing trip at the end of June, assuming the show would stay true to form as an early/mid-June event. Still, having to endure salmon and halibut fishing in Alaska rather than slogging around Moscone Center, I can’t pretend to be too disappointed; I’ll be thinking of you all 😎.… Read More

Thermal considerations have always been a concern in electronic systems but to a large extent these could be relatively well partitioned from other concerns. Within a die you analyze for mean and peak temperatures and mitigate with package heat-sinks, options to de-rate the clock, or a variety of other methods. At the system level… Read More