Field-Programmable Gate Arrays (FPGAs) have long been celebrated for their unmatched flexibility and programmability compared to Application-Specific Integrated Circuits (ASICs). And the introduction of Embedded FPGAs (eFPGAs) took these advantages to new heights. eFPGAs offer on-the-fly reconfiguration capabilities,… Read More

Tag: reconfigurable

Why Software Rules AI Success at the Edge

It is an unavoidable fact that machine learning (ML) hardware architectures are evolving rapidly. Initially most visible in datacenters (many hyperscalars have built their own AI chips), the trend is now red-hot in inference engines for the edge, each spinning new ground-breaking methods. Markets demand these advances to … Read More

High Efficiency Edge Vision Processing Based on Dynamically Reconfigurable TPU Technology

While many tough problems relating to computing have been solved over the years, vision processing is still challenging in many ways. Cheng Wang, Co-Founder and CTO of FlexLogix Technologies gave a talk on the topic of edge vision processing at Linley’s Spring 2022 conference. During that talk he references how Gerald Sussman… Read More

PCIe Gen5 Interface Demo Running on a Speedster7t FPGA

The major market drivers of today all have one thing in common and that is the efficient management of data. Whether it is 5G, hyperscale computing, artificial intelligence, autonomous vehicles or IoT, there is data creation, processing, transmission and storage. All of these aspects of data management need to happen very fast.… Read More

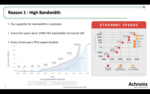

Five Reasons Why a High Performance Reconfigurable SmartNIC Demands a 2D NoC

As part of their webinar series, SemiWiki hosted one in June with the title “Five Reasons Why a High Performance Reconfigurable SmartNIC Demands a 2D NoC.” The talk by given by Scott Schweitzer, Sr. Manager, Product Planning at Achronix. Scott is a lifelong technology evangelist and focuses on recognizing technology trends and… Read More

One chip and the MCU variant challenge disappears

Merchant microcontrollers are usually made available in a wide range of variants based on one architecture with different peripheral payloads and packaging options. A couple of companies, notably Cypress with their PSoC families and Silicon Labs with the EFM8 Laser Bee… Read More

Flex Logix validating EFLX on TSMC 40ULP

Flex Logix has been heads-down for the last several months working toward customer implementations of their EFLX reconfigurable RTL IP cores. Today, they’ve announced a family of 10 hard IP cores ready in TSMC 40ULP, and provided an update to their roadmap for us.… Read More

S2C opens up FPGA prototyping for PCIe fabrics

Reconfigurable computing began with FPGA cards dropped into expansion slots in workstations. FPGA-based prototyping vendors tended away from that model as interconnect speeds rose and cabling complexity between modules increased. Much faster PCIe interfacing and bigger FPGAs mean revisiting the concept.… Read More

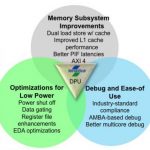

Reconfigurable redefined with embedded FPGA core IP

On November 1, 1985, before anyone had heard the phrase field programmable gate array, Xilinx introduced what they called a “new class of ASIC” – the XC2064, with a whopping 1200 gates. Reconfigurable computing was born and thrived around the RAM-based FPGA, whose logic and input/output pins could be architected into a variety… Read More

Putting the Ten in Tensilica

Chris Rowen of Cadence’s Tensilica announced the tenth generation of the Xtensa customizable processor at the Linley Microprocessor Conference yesterday. Chris was one of the founders of Tensilica…back in 1997. I believe that the first version was released in 1999. Over the years the Tensilica business changed.… Read More