Xilinx has delivered not only “the biggest FPGA on the planet”, but what it claims is currently the world’s largest integrated circuit: the Virtex UltraScale VU440, with 19 billion transistors fabbed in TSMC 20nm. The list of first customers to receive parts says a lot about the state of SoC design today, and the vital role FPGA-based… Read More

Tag: prototyping

Prototyping Kits to Accelerate IP Development & Integration into SoCs

With growing SoC size, complexity, software and hardware content in it and shrinking time-to-market, the SoC design completion in time has become increasingly dependent on IP which need to be sourced (internally or externally), customized according to the design need and integrated together into the SoC. While IP providers… Read More

Optimize Your Interconnect & Design at System Level for Best Results

As the SoC design size, complexity and functionality keeps on increasing with multiple IPs packed together and design time and time-to-market keeps on decreasing amid critical constraints on PPA, there is no other alternative than to do the design first-time-right not to miss the window of opportunity. And that could be possible… Read More

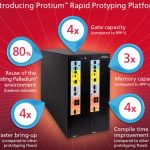

Palladium’s Little Brother Protium

Today, Cadence announced Protium, a new FPGA prototyping platform for software development. During development of an SoC, the most appropriate methodology changes. In the early days, developing RTL, the primary tool is simulation. Then, as the blocks get bigger or as the whole chip starts to come together, typically simulation… Read More

Accelerating SoC Simulation Times

There never seems to be enough time in a SoC project to simulate all of the cycles and tests that you want to run, so any technique to accelerate each run is welcomed. You can just wait for your software-based RTL simulator to finish running, or you can consider using a hardware-based accelerator approach. I learned more about one such… Read More

Zynq out of the box, in FPGA-based prototyping

Roaming around the hall at ARM TechCon 2012 left me with eight things of note, but one of the larger ideas showing up everywhere is the Xilinx Zynq. Designers are enthralled with the idea of a dual-core ARM Cortex-A9 closely coupled with programmable logic.… Read More

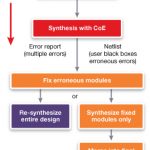

Second FPGA to the right, and straight on ‘til it works

In a fantasy world where there were no coding errors or integration issues, FPGA designs would fly straight through synthesis easily and quickly. Maybe that world does exist somewhere. For the rest of us, who have experienced the agony of running a large FPGA design – again – only to find another error and have to start over, there … Read More

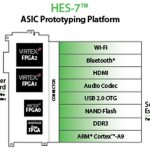

ASIC Prototyping with 4M to 96M Gates

I’ve used Aldec tools like their Verilog simulator (Riviera PRO) when teaching a class to engineers at Lattice Semi, so to get an update about the company I spoke with Dave Rinehart recently by phone. A big product announcement by Aldec today is for their ASIC prototyping system with a capacity range of 4 Million to 96 Million… Read More

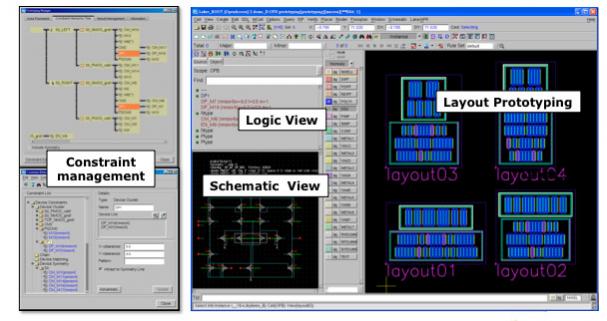

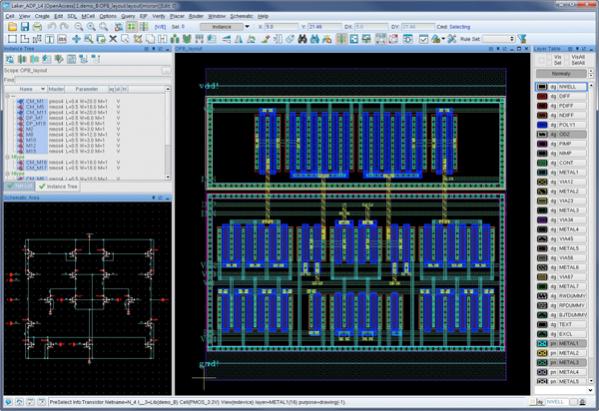

Laker Analog Prototyping

Over the years many attempts have been made to increase the level of automation in analog design. Most of these have not been especially successful. Probably part of the reason was inadequate technology but also there is an attitude that “real” analog designers design polygons on the bare silicon. I think two things… Read More

Laker Wobegon, where all the layout is above average

TSMC’s technnology symposium seems to be the new time to make product announcements, with ARM and Atrenta yesterday and Springsoft today.

There is a new incarnation of Springsoft’s Laker layout family, Laker[SUP]3[/SUP] (pronounced three, not cubed). The original version ran on its own proprietary database.… Read More