Engineers are always looking to improve the efficiency of how they work, but don’t want to sacrifice accuracy in the process. This is true in the world of semiconductor process development, where traditional build-and-test cycles are both time and resource intensive. But what if there was a way to do certain steps in a ‘virtual’… Read More

Tag: process variation

Process Variation is a Yield Killer!

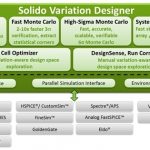

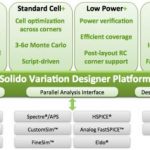

With the insatiable wafer appetites of the fabless semiconductor companies in the mobile space, yield has never been more critical. The result being better EDA tools every year and this blog highlights one of the many examples. It has been a pleasure writing about Solido Design Automation and seeing them succeed amongst the foundries… Read More

First FinFETs Manufactured at #50DAC!

This was my 30[SUP]th[/SUP] DAC and the second most memorable. The most memorable was my second DAC (1985) in Las Vegas with my new bride. We had a romantic evening ending with ice cream sundaes at midnight that we still talk about. This year SemiWiki had Dr. Paul McLellan, Dr. Eric Esteve, Daniel Payne, Don Dingee, Randy Smith, and… Read More

Winning in Monte Carlo: Managing Simulations Under Variability and Reliability

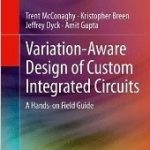

I recently talked to Trent McConaghy about his book on variation-aware design of custom ICs and the #50DAC tutorial we are doing:

Winning in Monte Carlo: Managing Simulations Under Variability and Reliability.

Trent is the Solido Chief Technology Officer, an engaging speaker, one of the brightest minds in EDA, and someone who… Read More

Solido CEO on 20nm/16nm TSMC and GLOBALFOUNDRIES Design Challenges

EDA needs more CEOs like Amit Gupta. Solido, which is now profitable, is his second AMS EDA company. The first, Analog Design Automation (ADA), was purchased by Synopsys for a hefty multiplier. Prior to becoming an EDA entrepreneur, Amit was product manager for the wireless group at Nortel and a hardware engineer for the RF communications… Read More

TSMC ♥ Solido

Process variation has been a top trending term since SemiWiki began as a result of the articles, wikis, and white papers posted on the Solido landing page. Last year Solido and TSMC did a webinar together, an article in EETimes, and Solido released a book on the subject. Process variation is a challenge today at 28nm and it gets worse… Read More

Cadence ♥ TSMC

TSMC has been investing in the fabless semiconductor ecosystem for 25+ years and that is why they are the #1 foundry and lead this industry (my opinion). I’m a big fan of joint webinars. Not only is it collaboration open to the masses, it is a close collaboration between the two sponsoring companies. Having worked on the TSMC… Read More

Variation-aware IC Design

We’ve blogged before about Layout Dependent Effects (LDE) on SemiWiki and how it further complicates the IC design and layout process, especially at 28nm and lower nodes because the IC layout starts to change the MOS device performance. There’s an interesting webinarfrom Cadence on Variation-aware IC Design, … Read More

Variation-Aware Design: A Hands-on Field Guide

IC designers using advanced nodes are acutely aware of how variation effects in the silicon itself are causing increased analysis and design efforts in order to yield chips at acceptable levels. Four authors from Solidoare so passionate about this topic that they combined their years of experience into a book that I had a chance… Read More

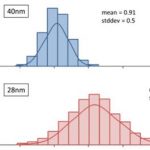

Variation at 28-nm with Solido and GLOBALFOUNDRIES

At DAC 2012 GLOBALFOUNDRIES and Solido presented a user track poster titled “Understanding and Designing for Variation in GLOBALFOUNDRIES 28-nm Technology” (as was previously announced here). This post describes the work that we presented.

We set out to better understand the effects of variation on design at 28-nm. In particular,… Read More