I’ll never forget the shock when I upgraded from a Feature Phone to my first Android-powered SmartPhone, because all of a sudden my battery life went from 6 days down to only 1 day between charges. As a consumer, I really want my battery to last much longer than one day, so the race is on for mobile phone companies to design their… Read More

Tag: power

A Complete Scalable Solution for IP Signoff

In an SoC world driven by IP, where an SoC can have hundreds of IP (sourced not only from 3[SUP]rd[/SUP] party but also from internal business units which can have a lot of legacy) integrated together, it has become essential to have a comprehensive and standard method to verify and signoff the IP. Additionally, these checks must … Read More

FinFET Design for Power, Noise and Reliability

IC designers have been running analysis tools for power, noise and reliability for many years now, so what is new when you start using FinFET transistors instead of planar transistors? Calvin Chow from ANSYS (Apache Design) presented on this topic earlier in the summer through a 33 minutewebinar that has been archived. There is… Read More

How to Reduce Maximum Power at RTL Stage?

Of course that reduction has to stay throughout the design cycle up to layout implementation and fabrication. Since the advent of high density, mega functionality SoC designs at advanced nodes and battery life critical devices played by our fingertips, the gap between SoC power requirement and actual SoC power has only increased.… Read More

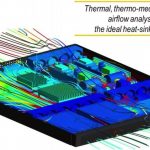

Electronic Thermal Management through Icepak

Last week my daughter was playing some games on my Google Nexus smartphone for a while when one of my friends called. When I picked up the phone, I couldn’t imagine it was so hot. There is no doubt; every electronic device today emits an order of magnitude higher heat than what it used to at most a decade ago. There is so much emphasis on … Read More

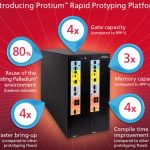

Palladium’s Little Brother Protium

Today, Cadence announced Protium, a new FPGA prototyping platform for software development. During development of an SoC, the most appropriate methodology changes. In the early days, developing RTL, the primary tool is simulation. Then, as the blocks get bigger or as the whole chip starts to come together, typically simulation… Read More

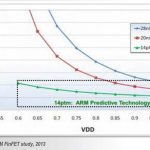

Xilinx has the Power Advantage over Altera

I thought I write about one of the most important subjects in FPGAs, that is power. Power of course is not just based on node size, and it is funny why so many people are concerned about node size. If not just as important is the architectural decisions that drive down power. Do you really care if your part is 16nm or 14nm? Or do you care more… Read More

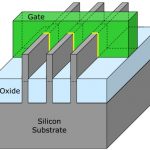

Intel & Ansys Enable 14nm Chip Production

In the semiconductor industry, it feels great to hear about the process technology shrinking to lower nodes along with innovative transistor structures that offer major gains in PPA (Power, Performance and Area). However, it requires huge investment of capital, time and effort from foundries to conceptualize, prototype and… Read More

Sensor Hub and Wearable Gestures

One of the challenges with the internet of things (IoT) is that many devices are both always on and battery powered (and not with a large battery). The responsibilities need to be split so that the device senses when it needs to wake up without requiring the application processor to be waking up all the time to make the decision since… Read More

Embedded Vision Summit

I was a the embedded vision conference last week. Jeff Beir, the founder of the embedded vision alliance gave an introduction to the field. The conference was much bigger than previous years and almost everyone is designing some sort of vision product. Half of your brain is used for vision so it goes without saying that vision requires… Read More