Yesterday was the first day of CDNLive. There were three keynotes. The first was by Lip-Bu Tan, Cadence’s CEO (and the Chairman of Walden International that he will be the first to remind you). The most interesting tidbit was that Cadence now has over 1000 people working on IP and that it represents 11% of their revenue. Then… Read More

Tag: power

IP for IoT: Thanks for the Memory

The Internet of Things (IoT) is clearly the buzzword of the moment, and like many catchy phrases it also tends to mean what you want it to mean, rolling up some things that exist like the automotive market or industrial automation, along with markets for things like wearables and healthcare that are largely in the future. But however… Read More

Analyzing Power Nets Early and Often, a New White Paper

One of the big challenges in designing ICs today is designing a robust power net capable of delivering necessary current levels to all areas of the die. Getting it wrong can, of course, lead to circuit failures that range from non-functional silicon, through intermittent performance and functional problems, to early EM-driven… Read More

Using NoCs to Reduce Power

Earlier this week I moderated a webinar at Sonics entitled NoC 102: Using SonicsGN to Address Low Power Requirements. Drew Wingard, the CTO of Sonics, presented it. It goes without saying that power is a major concern in SoC design, not just with chips for battery powered devices but also tethered devices. A major cost of ownership… Read More

Temperature Monitoring IP to Revamp SoCs

With increasing density and functionality of chips at extremely thin silicon and metal layers, temperature has become critical. The temperature situation can become worse with wireless enabled 24/7 power-on devices. In such a scenario, a device must manage its thermal profile dynamically to keep the temperature within tolerable… Read More

Analyzing Power Nets

One of the big challenges in a modern SoC is doing an accurate analysis of the power nets. Different layers of metal have very different resistance characteristics (since they vary so much in width and height). Even vias can cause problems due to high resistance. Typically power is distributed globally on high-level metal layers,… Read More

Components for Wearables, Making the IoT Real

The screenwriter William Goldman is famous for saying that in Hollywood “Nobody knows anything.” Meaning that there is simply no way for any of the people involved to be able to predict which movies will turn out to be hits and which will be flops. I think the internet of things (IoT) is going to be like that. There will … Read More

How to Optimize for Power at RTL

Last week I was traveling in Munich attending the MunEDA User Group meetingso I missed a live webinar on the topic of optimizing for power at RTL. I finally got caught up in my email this week and had time to view this 47 minute webinar, presented by Guillaume Boilletof Atrenta. He recommended using a combination of automatic, semi-automatic… Read More

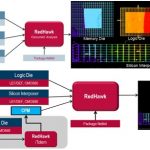

Solution for PI, TI & SI Issues in 3D-ICs

As we move towards packing more and more functionalities and increasing densities of SoCs, the power, thermal and signal integrity issues keep on rising. 3D-IC is a great concept to stack multiple dies on top of each other vertically. While it brings lot of avenues to package dies with multiple functions together, it has challenges… Read More

Simulation and Analysis of Power and Thermal Management Policies

Earlier this month I blogged about Power Management Policies for Android Devices, so this blog is part two in the series and delves into the details of using ESL-level tools for simulation and analysis. The motivation behind all of this is to optimize a power management system during the early design phase, instead of waiting until… Read More