The market demanded that gadgets it loves become ever more conscious of their power consumption, and chip designers responded with an array of clever techniques to cut IC power use. Unsurprisingly, these new techniques added to the complexity of IC verification. When you’re verifying a design that has 100+ separate power domains,… Read More

Tag: power

A Complete Simulation Platform for Mobile Systems

If we take an insight into the semiconductor industry, we can easily find that mobile systems are the main drivers of this industry. The Smartphone business has remained at the top since a good number of years. Although the Smartphone sales growth has started showing a sign of stagnation, it is still a main contributor with a solid… Read More

Older Nodes Get New Life With Ultra Low Power Variants for IoT

Ever since I can remember, and I’ve been in EDA since the early 80’s, new process development has largely focused on the latest nodes. Trailing nodes were quickly put into support mode. New nodes benefited the most from static and dynamic voltage reduction efforts, as well as improvements in flows and performance. Only a small number… Read More

A New Unified Power Solution at All Levels

When situation demands, multiple solutions appear with a slight lag of time. Similar is the story with estimating and optimizing power at SoC level. In the SoC era, power has become a critical criterion long ago, and there are tools available for power analysis and optimization. However, with more mobile and IoT (Internet of Things)… Read More

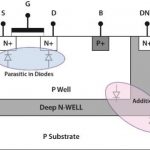

Build Low Power IoT Design with Foundation IP at 40nm

In a power hungry world of semiconductor devices, multiple ways are being devised to budget power from system to transistor level. The success of IoT (Internet of Things) Edge devices specifically depend on lowest power, lowest area, optimal performance, and lowest cost. These devices need to be highly energy efficient for sustained… Read More

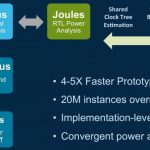

Power Analysis Needs Shift in Methodology

It’s been the case most of the time that until we hit a bottleneck situation, we do not realize that our focus is not at the right spot. Similar is the case with power analysis at the SoC level. Power has become equally if not more important than the functionality and other parameters of an SoC, and therefore has to be verified earlier … Read More

How PowerArtist Interfaces with Emulators

Last month in DAC I could see some of the top innovations in the EDA world. EDA is a key enabler for advances in semiconductor designs. Among a number of innovations worth mentioning (about which I blogged just after DAC), the integration of Mentor’s Veloce with ANSYS’ PowerArtist for power analysis of live applications caught my… Read More

How Emulation Enables Complex Power Intent Modeling

As the number of CPU, GPU, and IP is growing in an SoC, power management is becoming more and more a complex task in itself. A single tool or methodology may not be enough for complete power management and verification of an SoC. In an SoC, there can be multiple modes of operations involving hardware and software interactions, different… Read More

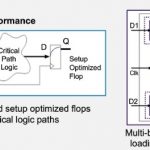

Power Management Gets Tricky in IP Driven World

Today, an SoC can have multiple instances of an IP and also instances of many different IPs from different vendors. Every instance of an IP can work in a separate mode and requires a dedicated power arrangement which may only be formalized at the implementation stage. The power intent, if specified earlier, will need to be re-generated… Read More

Samsung: the Journey to 14nm and 10nm

At the Samsung theatre (cutely named the Samsung Open Collaboration (SoC) theater) I watched a presentation by KK Lin on using DFM to bring up their 14nm and 10nm processes. And yes, they are real. Here is a picture I took of a 14nm wafer and a 10nm wafer. Samsung announced that they would ramp 10n to volume production by the end of next… Read More