Increasingly the challenge with SoCs, especially for mobile, is not getting the performance high enough but doing so in a power-efficient manner. Handheld devices running multiple apps need high-speed processors that consume extremely low levels of power both in operating and standby modes. In the server farm, the limit is … Read More

Tag: power

TSMC Theater Presentation: Apache

At the TSMC Theater Apache (don’t forget, now a subsidary of Ansys) talked about Emerging Challenges for Power, Signal and Reliability Verification on 3D-IC and Silicon Interposer Designs. The more I see about the costs and challenges of 20/22nm and below, the more I think that these 3D and 2.5D approaches are going to be … Read More

Customers Talk About Reliability, Low-Power and 3D

At DAC in San Francisco this year, Apache once again have a mixture of presentations by customers on their use of Apache tools and presentations by Apache themselves on their products. Most of the customer presentations are given just once, but the product presentations are given multiple times over the three days.

I think one of… Read More

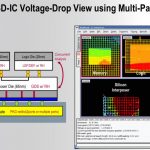

RedHawk: On to the Future

For many, maybe most, big designs, Apache’s RedHawk is the signoff tool for analyzing issues around power: electromigration, power supply droop, noise, transients and so on. But the latest designs have some issues: they are enormous (so you can’t just analyze them naively any more than you can run a Spice simulation… Read More

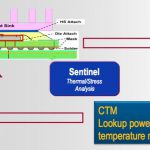

Designing for Reliability

Analyzing the operation of a modern SoC, especially analyzing its power distribution network (PDN) is getting more and more complex. Today’s SoCs no longer operate on a continuous basis, instead functional blocks on the IC are only powered up to execute the operation that is required and then they go into a standby mode, … Read More

Power Issues for Chip and Board: webinar

Last month Brian Bailey at EDN moderated an interesting webinar about power issues. Unusually, it combined two different domains: doing things by modeling and actually taking measurements off real chips and boards. The two participants were Arvind Shanmugavel from the Apache subsidiary of Ansys, and Randy White from Tektronix.… Read More

Power to the Drones

Unmanned systems are becoming indispensable to military forces and are used across all of land, sea and air. The generic name for such unmanned systems is UXS, usually UAS (air), UGS (ground) or UUS (underwater). The UAS is the most visible, both due to military strikes and the views of Japan after the Tsunami when areas were unreachable… Read More

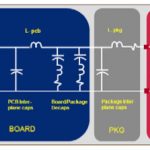

Chip-Package-System workshops

Chips, packages and circuit boards (systems, hence CPS) used to be three separate domains with their own tools that barely interacted at all. If you were lucky, reassigning a pin on a package wouldn’t have to be done manually in all 3 places. But now, from a signal integrity, noise, power point of view these three domains must… Read More

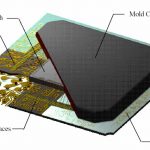

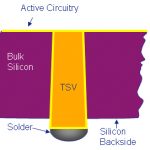

Challenges in 3D-IC and 2½D Design

3D IC design and what has come to be known as 2½D IC design, with active die on a silicon interposer, require new approaches to verification since the through silicon vias (TSVs) and the fact that several different semiconductor processes may be involved create a new set of design challenges

The power delivery network is a challenge… Read More

Nvidia’s Chris Malachowsky on "Watt’s next"

The video and slides of the CEDA lunch from a month or two ago are now (finally) up here. Chris Malachowsky presented “Watt’s next.” Chris is one of the founders of nVidia and is currently its senior VP of research. He started by talking a bit about the nVidia product line but moved on to talking about supercomputers… Read More