I can’t imagine that any SoC today is designed without taking intense interest in how much power the chip will consume, whether it is destined for a mobile phone or tethered in a cloud datacenter. One challenge with power is that adding features like voltage islands or power-down areas require changes to the netlist such as… Read More

Tag: power

Sanjiv Kaul: Is HLS About to Take Off?

At the end of last week I talked to Sanjiv Kaul, the new CEO of Calypto. Just to give a little background for those that haven’t been following along at home, Calypto was founded to try and solve the very hard problem of sequential logical equivalence checking (mostly by people from the engineering team that I managed at Ambit).… Read More

High and Low: High Level Synthesis and Low Power

It is so widely accepted that it is already a cliche to say that “power is the new timing.” With more and more chips, the major challenge is not so much to meet timing but to meet timing without blowing out the power budget. Otherwise, you could just crank up the clock rate.

I’m going to be lazy so you can insert your … Read More

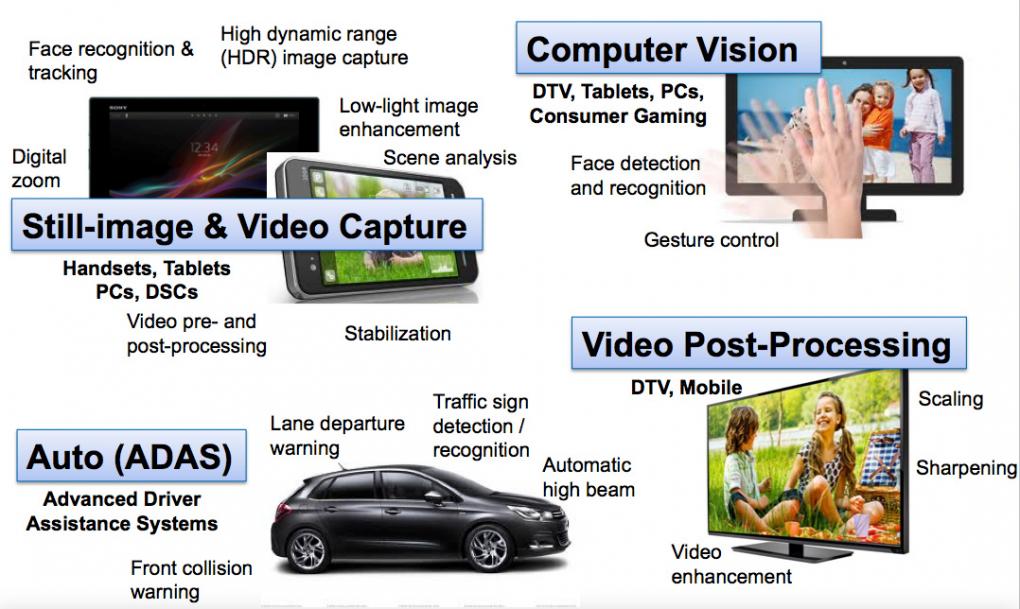

Video? Tensilica Has You Covered

Video is a huge growing area and advanced imaging applications are becoming ubiquitous. By “advanced” I mean more than just things like cameras in your smartphone. There is lots more coming, from high-dynamic range (HDR) photography, gesture recognition, more and more intelligent video in cars to keep us safe, … Read More

Sanjiv Kaul is New CEO of Calypto

Calypto announced that Sanjiv Kaul is the new CEO. I first met Sanjiv many years ago when he was still at Synopsys when I interviewed for a position there around the time I transitioned out of Compass and went back to the parent company VLSI. I forget what the position was. Then about three or four years ago when I did some work for Oasys… Read More

FD-SOI is Worth More Than Two Cores

This is the second blog entry about an ST Ericsson white-paper on multiprocessors in mobile. The first part was here.

The first part of the white-paper basically shows that for mobile the optimal number of cores is two. It is much better to use process technology (and good EDA) to run the processor at higher frequency rather than add… Read More

Cortex-A9 speed limits and PPA optimization

We know by now that clock speeds aren’t everything when it comes to measuring the goodness of a processor. Performance has direct ties to pipeline and interconnect details, power factors into considerations of usability, and the unspoken terms of yield drive cost.

My curiosity kicked in when I looked at the recent press release… Read More

Apache Power Artist Capabilities II

This is the second part of my discussion with Paul Traynar, Apache’s PowerArtist guru. The first part discussed sequential reduction capabilities. Part I was here.

There are two big challenges with doing power analysis at the RTL level. Firstly, how do you get an accurate enough model of what the design will dissipate given… Read More

Sequential Power Optimization

Calypto has an interesting webinar coming up about Minimizing RTL Power Through Sequential Analysis. It is next Tuesday December 4th at 11am.

Insert standard paragraph about how power is the new timing, everyone worries about power, battery life in smartphones, half-empty datacenters.

You probably already know about clock… Read More

Power and Reliability Challenges

Last week I attended the Ansys/Apache seminars on “Dimensions of Electronic Design.” The two big challenges as we go down to 28nm and 20nm and below are keeping power manageable and keeping reliability up.

The big challenge with power is that we can put so much stuff on a die and clock it so fast that the power is exceeding… Read More