You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

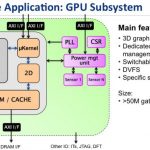

Last week I talked to Eileen You of Samsung-SSI to get a preview on what they will be talking about at Apache’s customer theater at DAC. Their presentation is titledThe Life of PI: SoC Power Integrity from Early Estimation to Design Sign-off. The ‘PI’ stands for Power Integrity.

Samsung-SSI’s operations… Read More

AMD Reduces Power by 20%by Paul McLellan on 05-16-2013 at 4:12 pmCategories: EDA

Steve Kommrusch of AMD wrote a white paper with Calypto on how AMD reduced power by 20% on the Jaguar SoC using Calypto’s PowerPro. Dan Nenni blogged about it on SemiWiki back in February here. And now, drumroll, Steve will present the story live and in person at DAC, on Monday June 3rd at 3pm and on Wednesday June 5th at 11am. This… Read More

I went to some of the JEDEC mobile conference a couple of weeks ago. The opening keynote was by Richard Wietfeld of Qualcomm called The Need for Speed.

He emphasized that smartphones are really setting the pace these days in all things mobile and internet. Over 1/3 of access is on smartphones now. Over 4/5 of searches on smartphones… Read More

Today, Jasper announced their new Jasper-Gold Low Power Verification App. This is focused on verifying low power designs with multiple power domains, voltage islands, power shutoff, clock shutoff, and all the other techniques used for reducing power. Of course power is the main driver of SoC design these days, whether it is for… Read More

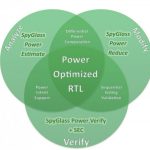

As Julius Caesar said, “Gallia est omnis divisa in partes tres.” All Gaul is divided into 3 parts. Calypto is similar with three product lines that work together to provide a system level approach to SoC design. Two of those product lines are not unique, in the sense that similar capabilities are available from a handful… Read More

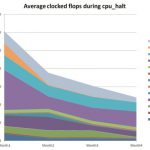

Given today’s design requirements with respect to low power, there is increasing focus on the contribution to total power made by a design’s clock trees. The design decisions made by the front-end team to achieve high performance without wasting power must be conveyed to back-end team. This hand-off must be accurate… Read More

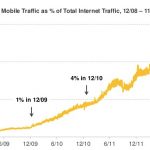

Mobile devices are taking over the world. If you want lots of graphs and data then look at Mary Meeker’s presentation that I blogged about earlier this week. The graph on the right is just one datapoint, showing that mobile access to the internet is probably up to about 15% now from a standing start 5 years ago.

Of course, one obvious… Read More

I hosted a webinar today for GlobalFoundries. Yes, I know that today was TSMC’s Technology Symposium, we weren’t that smart when we picked the date. It was basically a “fireside chat” with me as the moderator asking the questions and Paul Colestock and Aabid Husain as my guests. We actually did it at Cadence… Read More

RTL Power Optimizationby Paul McLellan on 04-09-2013 at 10:23 amCategories: EDA

More so than most aspects of design, power reduction suffers from a paradox that early in the design cycle when the gains are the largest, the accuracy of power estimation is the lowest, and then late in the design cycle, when everything is known pretty much exactly it is too late to make anything other than trivial optimizations. … Read More

The world is analog and despite enormous SoCs in the most leading-edge process node being the most glamorous segment of the semiconductor industry, it turns out that one of the fastest growing segments is actually analog and power chips in older process technologies. Overall, according to Semico, analog and power ICs, including… Read More