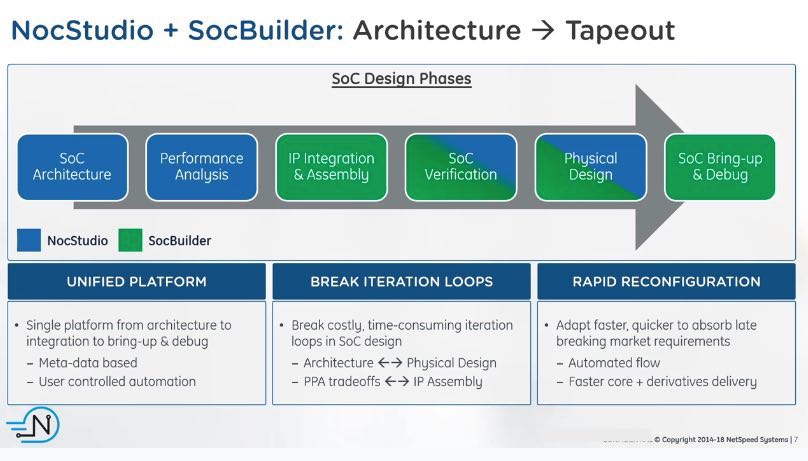

A large part of the effort in designing SOCs has shifted to the integration of their constituent IP blocks. Many IP blocks used in SOCs come as ready to use components and the real work has become making them work together. Network on Chip (NoC) has been a huge help in this task, handling the interconnections between blocks and planning… Read More

Tag: performance

Netspeed and NSITEXE talk about automotive design trends at 55DAC

DAC is where both sides of the design equation come together for discussion and learning. This is what makes attending DAC discussion panels so interesting; you are going to hear from providers of tools, methodologies and IP as well as those who need to use them to deliver working solutions. There are few places where the interplay… Read More

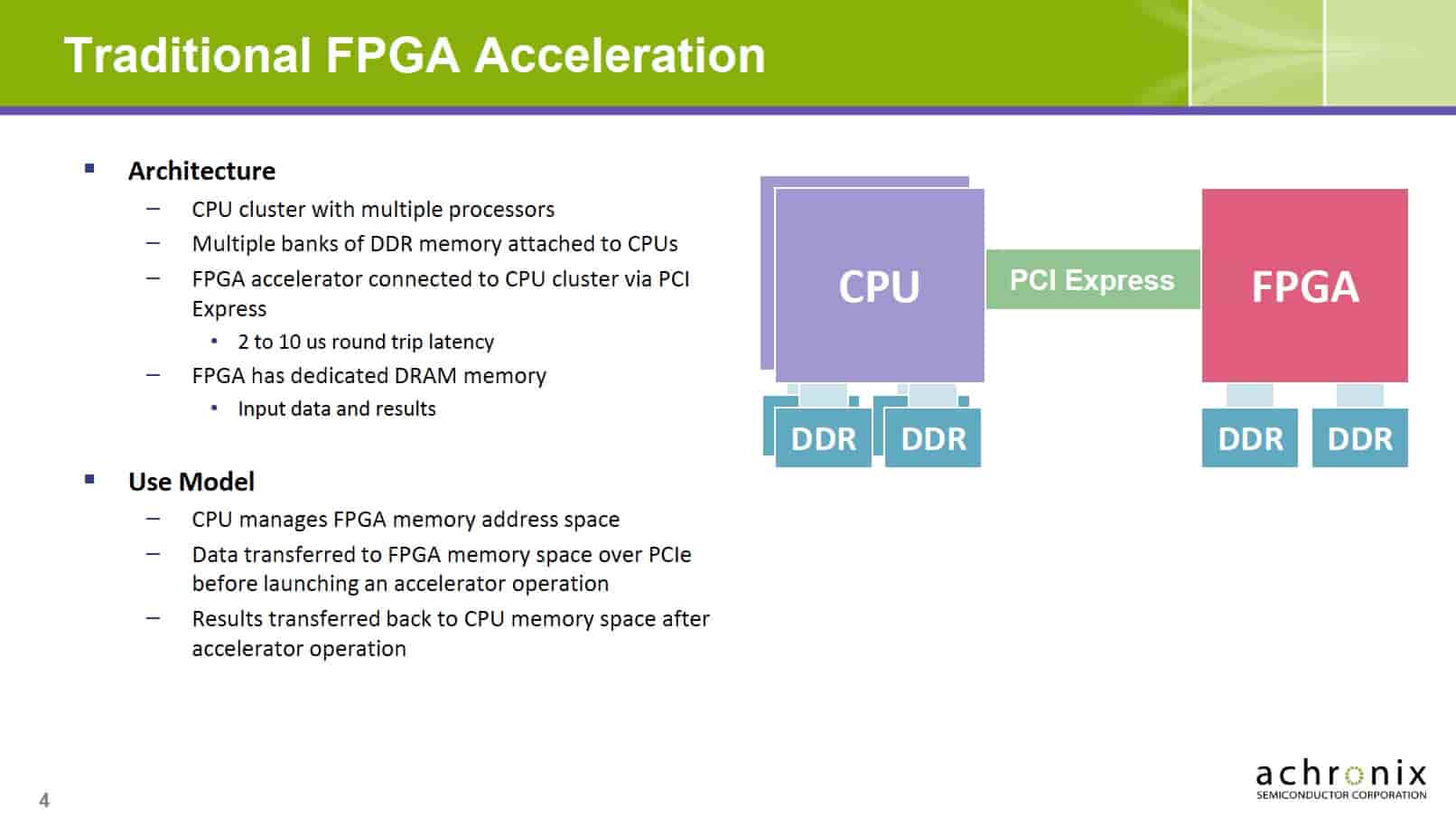

The lofty rise of the lowly FPGA

FPGA programmable logic has served in many capacities since it was introduced back in the early 80’s. Recently, with designers looking for innovative ways to boost system performance, FPGA’s have moved front and center. This initiative has taken on new urgency with the slowing down of process node based performance gains. The… Read More

HBM offers SOC’s dense and fast memory options

Dual in-line memory modules (DIMM’s ) with double data rate synchronous dynamic random access memory (DDR SDRAM) have been around since before we were worried about Y2K. Over the intervening years this format for provisioning memory has evolved from supporting DDR around 1995, to DDR1 in 2000, DDR2 in 2003, DDR4 in 2007 and DDR4… Read More

How to nail your PPA tradeoffs

How do you ensure your design has been optimized for power, performance, and area? I posed this question to Mentor’s Group Director of Marketing, Sudhakar Jilla and product specialist Mark Le. They said that finding the PPA sweet spot is still often done by trial and error – basically serial experiments with various input parameters… Read More

Webinar: A Tool for Process and Device Evaluation

Not only are foundries continuing to introduce processes at new advanced nodes, they are frequently updating or adding processes at existing nodes. There are many examples that illustrate this well. TSMC now has 16FF, 16FF+ and now 16FFC. They are also announcing 10nm and 7nm processes. In addition, they are going back to older… Read More

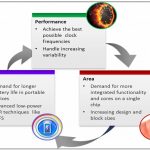

SoCs in New Context Look beyond PPA

If we look back in the last century, performance and area were two main criteria for semiconductor chip design. All design tools and flows were concentrated towards optimizing those two aspects. As a result, density of chips started increasing and power became a critical factor. Now, Power, Performance and Area (PPA) are looked… Read More

How to Benchmark a Processor

How do you benchmark a processor? It seems like it should be easy, just run some code and see how fast it is. Traditionally processors were indeed benchmarked by raw performance like GMACS, GFLOPS, memory bandwidth and so on. But in today’s world where systems have become very complex and applications very compute intensive, the… Read More

Cortex-A9 speed limits and PPA optimization

We know by now that clock speeds aren’t everything when it comes to measuring the goodness of a processor. Performance has direct ties to pipeline and interconnect details, power factors into considerations of usability, and the unspoken terms of yield drive cost.

My curiosity kicked in when I looked at the recent press release… Read More

Analyzing Cortex Performance

CPAK sounds like something politicians create to collect money, but in fact it is a Carbon Performance Analysis Kit. It consists of models, reference platform, initialization software (for bare metal CPAKs) or OS binary (for Linux and Android based CPAKs). They are (or will soon be) available for ARM Cortex A9, ARM Cortex A15 and… Read More