Due to the overwhelming response, here is the first part of the webinar that I did with S2C and a link to the replay. Richard Chang, Vice President of Engineering at S2C did the technical part of the webinar. Richard has a Masters degree in Electrical engineering from the University at Buffalo and more than 20 years experience designing… Read More

Tag: pcie

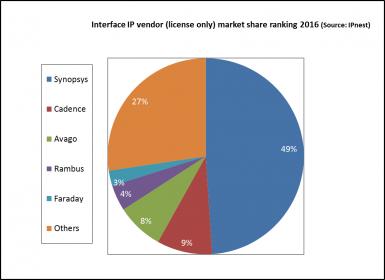

Worldwide Interface IP Revenue Grew by 13.5% in 2016 (Source: IPnest)

IPnest has released the 9[SUP]th[/SUP] version of the Interface IP Survey, ranking by protocol the IP vendors addressing the Interface segments: USB, PCI Express, (LP)DDRn, MIPI, Ethernet & SerDes, HDMI/DP and SATA. When the 1[SUP]st[/SUP] version has been issued in 2009, the IP segment was weighting $225 million and the… Read More

The Interface IP Market has Grown to $530 Million!

According with IPnest, the Interface IP market, including USB, PCI Express, (LP)DDRn, HDMI, MIPI and Ethernet IP segments, has reached $532 million in 2016, growing from $472 million in 2015. This is an impressive 13% Year-over-Year growth rate, and 12% CAGR since 2012!

Who integrate functions to interface a chip with others … Read More

Virtualizing ICE

The defining characteristic of In-Circuit-Emulation (ICE) has been that the emulator is connected to real circuitry – a storage device perhaps, and PCIe or Ethernet interfaces. The advantage is that you can test your emulated model against real traffic and responses, rather than an interface model which may not fully capture… Read More

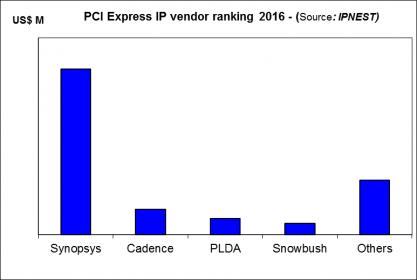

The IP Paradox: Sales are growing despite Semi Consolidation

IPnest is launching the “Interface IP Survey” since 2009, and we did it last September again. To build the survey as accurately as possible, I have followed the “divide and conquer” strategy. Interface protocols are varied, ranging from PCI Express, USB, or Ethernet, to memory controller (DDR3, DDR4, LPDDR3, LPDDR4 and more) … Read More

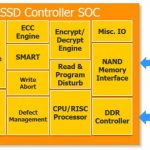

New Frontiers in the Storage System Market Call for the Best of ICE and Virtual Emulation

The storage market has reached what Andy Grove once described as “…a strategic inflection point.”[1] This is the stage in the life of a business when its fundamentals are about to change.

Changing fundamentals in the storage market—where solid state drives (SSD) are now at the forefront of multiple storage applications,… Read More

Design IP Growth Is Fueling 94% of EDA Expansion

Last June, the ESD Alliance (ESDA) has released Q1 2016 results for EDA (CAE, PCB & MCM and IC Physical), Silicon IP (SIP) and Services. Not a surprise for Semiwiki readers since 2013, the SIP category is recognized as the largest with $689 million revenues for the quarter, and four-quarters moving average increasing by 11.6… Read More

EDAC Name Changing for ESDA, but what about IP ?

The EDA Consortium (EDAC) has changed name for Electronic Systems Design Alliance (ESD Alliance). That’s a good reminder that IC are developed (thanks to Design Automation) to be integrated into a System. A wide design ecosystem support system development, including embedded software, design intellectual property (IP), … Read More

Aldec reprograms HES7 for AXI4 speed

FPGA-based prototyping firms are all grappling with the problem of higher speed connectivity between a development host and their hardware. Aldec is announcing their solution at DVCon 2016, turning to an AMBA AXI4 interface bridged into a host with PCIe x8.

Faster host interfaces deliver dual benefits in FPGA-based prototyping.… Read More

Interface IP year 2015: Winners and Losers

The global Interface IP market is still growing in 2015, no doubt about it. It’s interesting to zoom in the various protocols to check their respective behavior. Which protocol generates an IP business growing more than the average market? Which protocol generates a disappointing IP business? In other words, which are the winners… Read More