Before the advent of the digitized society and computer chips, things that needed protection were mostly hard assets such as jewelry, coins, real estate, etc. Administering security was simple and depended on strong guards who provided security through physical means. Then came the safety box services offered by financial … Read More

Tag: pcie

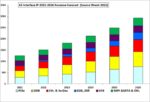

High-End Interconnect IP Forecast 2022 to 2026

The Interface IP market has grown with 21% CAGR from 2017 to 2021 and we review the part of this market restricted to the high-end of PCIe, DDR, Ethernet and D2D IP made of PHY and controller targeting the most advanced technology nodes and latest protocol release. We will show that an IP vendor focusing investment on the high-end interconnect… Read More

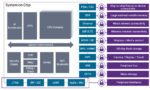

Integrating High Speed IP at 5nm

Introduction:

The advancements in deep submicron technology and adding multiple functionalities to reduce costs combined with scaling existing operations means that SoC designs become ever more complex. The biggest driving factors to go below the 16nm process node are the decrease in power and the increase in performance … Read More

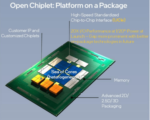

UCIe Specification Streamlines Multi-Die System Design with Chiplets

Over the last few years, the design of application-specific ICs as well as high-performance CPUs and other complex ICs has hit a proverbial wall. This wall is built from several issues: first, chip sizes have grown so large that they can fill the entire mask reticle and that could limit future growth. Second, the large chip size impacts… Read More

Interface IP in 2021: $1.3B, 22% growth and $3B in 2026

If you want to remember the key points for Interface IP in 2021, just consider $1.3B, 22%, $3B. Interface IP category has generated $1 billion 300 million in 2021, or 22.7% year to year growth, thanks to high runner protocols PCIe, DDR memory controller and Ethernet/SerDes. Even more impressive is the forecast, as IPnest predict… Read More

CXL Verification. A Siemens EDA Perspective

Amid the alphabet soup of inter-die/chip coherent access protocols, CXL is gaining a lot of traction. Originally proposed by Intel for cross-board and cross-backplane connectivity to accelerators of various types (GPU, AI, warm storage, etc.), a who’s who of systems and chip companies now sits on the board, joined by an equally… Read More

Verifying Inter-Chiplet Communication

Chiplets are hot now as a way to extend Moore’s Law, dividing functionality across multiple die within a single package. It’s no longer practical to jam all functionality onto a single die in the very latest processes, exceeding reticle limits in some cases and in others straining cost/yield. This is not an academic concern. Already… Read More

Stop-For-Top IP Model to Replace One-Stop-Shop by 2025

…and support the creation of successful Chiplet business

The One-Stop-Shop model has allowed IP vendors of the 2000’s to create a successful IP business, mostly driven by consumer application, smartphone or Set-Top-Box. The industry has dramatically changed, and in 2020 is now driven by data-centric application (datacenter,… Read More

SoC Application Usecase Capture For System Architecture Exploration

Sondrel is the trusted partner of choice for handling every stage of an IC’s creation. Its award-winning define and design ASIC consulting capability is fully complemented by its turnkey services to transform designs into tested, volume-packaged silicon chips. This single point of contact for the entire supply chain… Read More

Benefits of a 2D Network On Chip for FPGAs

The reason people love FPGAs for networking and communications applications is because they offer state of the art high speed interfaces and impressive parallel processing power. The problem is that typically a lot of the FPGA fabric resources are used simply to move the data on or off and across the chip. Achronix has cleverly … Read More