No, I’m not going to talk about in-memory-compute architectures. There’s interesting work being done there but here I’m going to talk here about mainstream architectures for memory support in Machine Learning (ML) designs. These are still based on conventional memory components/IP such as cache, register files, SRAM and various… Read More

Tag: noc

Qualcomm Intel Facebook and Semiconductor IP

What does Qualcomm, Intel, and Facebook have in common? Well, for one thing they all bought network onchip communications (NoC) IP companies. As I have mentioned before, semiconductor IP is the foundation of the fabless semiconductor ecosystem and I believe this trend of acquisitions will continue. So, if you are going to start… Read More

Why High-End ML Hardware Goes Custom

In a hand-waving way it’s easy to answer why any hardware goes custom (ASIC): faster, lower power, more opportunity for differentiation, sometimes cost though price isn’t always a primary factor. But I wanted to do a bit better than hand-waving, especially because these ML hardware architectures can become pretty exotic, so … Read More

Disturbances in the AI Force

In the normal evolution of specialized hardware IP functions, initial implementations start in academic research or R&D in big semiconductor companies, motivating new ventures specializing in functions of that type, who then either build critical mass to make it as a chip or IP supplier (such as Mobileye – intially)… Read More

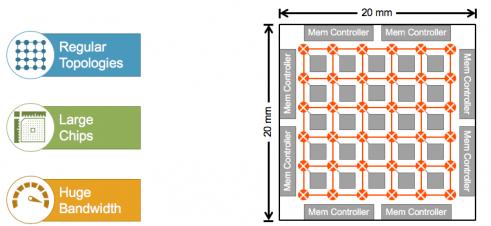

On-Chip Networks at the Bleeding Edge of ML

I wrote a while back about some of the more exotic architectures for machine learning (ML), especially for neural net (NN) training in the data center but also in some edge applications. In less hairy applications, we’re used to seeing CPU-based NNs at the low end, GPUs most commonly (and most widely known) in data centers as the workhorse… Read More

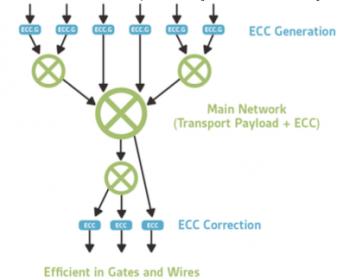

Supporting ASIL-D Through Your Network on Chip

The ISO 26262 standard defines four Automotive Safety Integrity Levels (ASILs), from A to D, technically measures of risk rather than safety mechanisms, of which ASIL-D is the highest. ASIL-D represents a failure potentially causing severe or fatal injury in a reasonably common situation over which the driver has little control.… Read More

Netspeed and NSITEXE talk about automotive design trends at 55DAC

DAC is where both sides of the design equation come together for discussion and learning. This is what makes attending DAC discussion panels so interesting; you are going to hear from providers of tools, methodologies and IP as well as those who need to use them to deliver working solutions. There are few places where the interplay… Read More

Safety in the Interconnect

Safety is a big deal these days, not only in automotive applications, but also in critical infrastructure and industrial applications (the power grid, nuclear reactors and spacecraft, to name just a few compelling examples). We generally understand that functional blocks like CPUs and GPUs have to be safe, but what about the … Read More

Machine Learning Neural Nets and the On-Chip Network

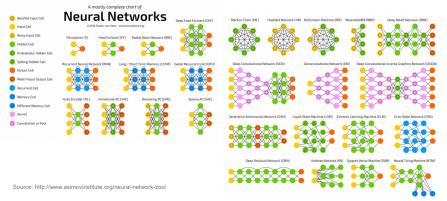

Machine learning (ML), and neural nets (NNs) as a subset of ML, are blossoming in all sorts of applications, not just in the cloud but now even more at the edge. We can now find them in our phones, in our cars, even in IoT applications. We have all seen applications for intelligent vision (e.g. pedestrian detection) and voice recognition… Read More

CES: An Exhibitor’s Takeaway

There are few tech promises these days as prominent as those surrounding driverless cars (trucks, buses, …). But thanks to always-on media amplifiers, it’s not always easy to separate potential from reality. I recently talked to Kurt Shuler, VP Marketing at Arteris, who shared his view after returning from this year’s CES. Kurt… Read More