With over 30 years of experience in sales and marketing of semiconductors and electronic components, Mr. Shoichi Teshiba has worked across a broad range of industries including storage, servers, networking, consumer electronics, industrial equipment, and automotive. Combining deep insight into both domestic and global… Read More

Tag: networking

Alchip is Golden, Keeps Breaking Records on Multiple KPIs

I don’t know the story behind the name Alchip. I’ve been asking this question ever since its founding in 2003 and still haven’t found the answer. Wikipedia sometimes provides insights and stories behind names of companies, products and services but I couldn’t find any regarding the name Alchip. One thing is for sure. After its consistent… Read More

Design IP Sales Grew 20.2% in 2022 after 19.4% in 2021 and 16.7% in 2020!

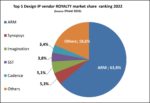

Design IP revenues had achieved $6.67B in 2022, after $5.56B in 2021, or 20.2% growth after 19.4% in 2021 and 16.7% in 2020. IPnest has released the “Design IP Report” in April 2023, ranking IP vendors by category (CPU, DSP, GPU & ISP, Wired Interface, SRAM Memory Compiler, Flash Memory Compiler, Library and I/O, AMS, Wireless… Read More

ARM Turns up the Heat in Infrastructure

I don’t know if it was just me but I left TechCon 2017 feeling, well, uninspired. Not that they didn’t put on a good show with lots of announcements, but it felt workman-like. From anyone else it would have been a great show, but this is TechCon. I expect to leave with my mind blown in some manner and it wasn’t. I wondered if the SoftBank … Read More

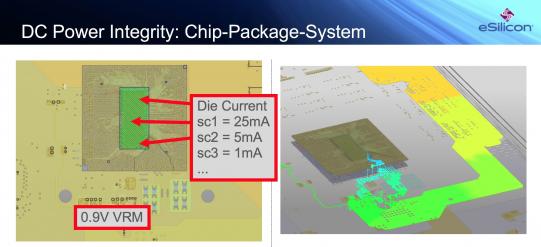

Chip, Package, System Analysis – A User View

While I missed ANSYS (and indeed everyone else) at DAC this year, I was able to attend the ANSYS Innovation Conference last week at the Santa Clara Convention Center. My primary purpose for being there was to listen to a talk by eSilicon which I’ll get to shortly, but before that I sat through a very interesting presentation on the growing… Read More

Platform ASICs Target Datacenters, AI

There is a well-known progression in the efficiency of different platforms for certain targeted applications such as AI, as measured by performance and performance/Watt. The progression is determined by how much of the application can be run with specialized hardware-assist rather than software, since hardware can be faster… Read More

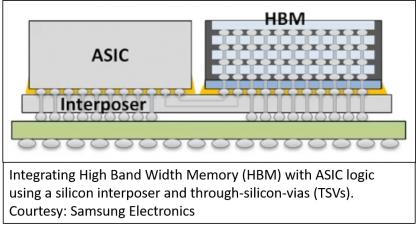

High Performance Ecosystem for 14nm-FinFET ASICs with 2.5D Integrated HBM2 Memory

High Bandwidth Memory (HBM) systems have been successfully used for some time now in the network switching and high-performance computing (HPC) spaces. Now, adding fuel to the HBM fire, there is another market that shares similar system requirements as HPC and that is Artificial Intelligence (AI), especially AI systems doing… Read More

Networking and Formal Verification

I attended Oski’s latest Decoding Formal event a couple of weeks ago and again enjoyed a largely customer-centric view of the problems to which they apply formal, and their experiences in making it work for them (with Oski help of course). From an admittedly limited sample of two of these events, I find them very representative of… Read More

Open Silicon Delivers Silicon-Verified HBM2 IP-Subsystem on TSMC 16nm FF+

Open Silicon hosted a webinar today focusing on their High Bandwidth Memory (HBM) IP-subsystem product offering. Their IP-subsystem is based on the HBM2 standard and includes blocks for the memory controller, PHY and high-speed I/Os, all targeted to TSMC 16nm FF+ process. The IP-subsystem supports the full HBM2 standard with… Read More

Polishing Parallelism

The great thing about competition in free markets is that vendors are always pushing their products to find an edge. You the consumer don’t have to do much to take advantage of these advances (other than possibly paying for new options). You just sit back and watch the tool you use get faster and deliver better QoR. You may think that… Read More