You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

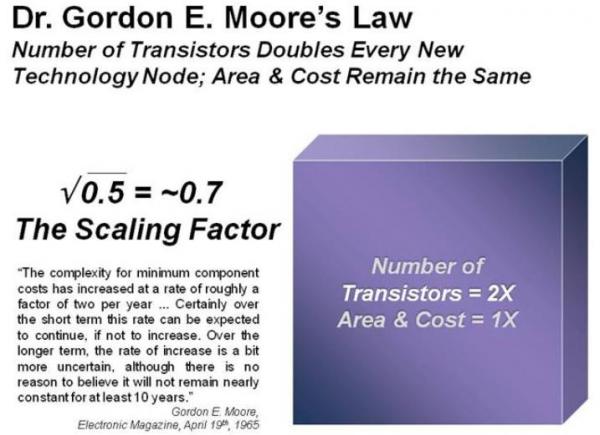

At the GSA silicon summit yesterday the first keynote was by Subramanian Iyer of IBM on Keeping Moore’s Law Alive. He started off by asking the question “Is Moore’s Law in trouble?” and answered with an equivocal “maybe.”

Like some of the other speakers during the day, he pointed out that … Read More

The first GSA Silicon Summit will address the complexity, availability and time-to-market challenges that the industry must overcome to enable low power, cost effective solutions to keep pace with Moore’s Law. With never ending customer demand of better, faster and cheaper, semiconductor manufacturers must continually… Read More

It has been a great conundrum to many of the 20[SUP]th[/SUP] century trained economists and Harvard’s Kennedy School of Government folks as to why a government led massive spending spree and Ben Bernanke’s non-stop printing presses can’t at least engender a mediocre economic recovery.

I blame 21st century Moore’s Law!

Today’s… Read More

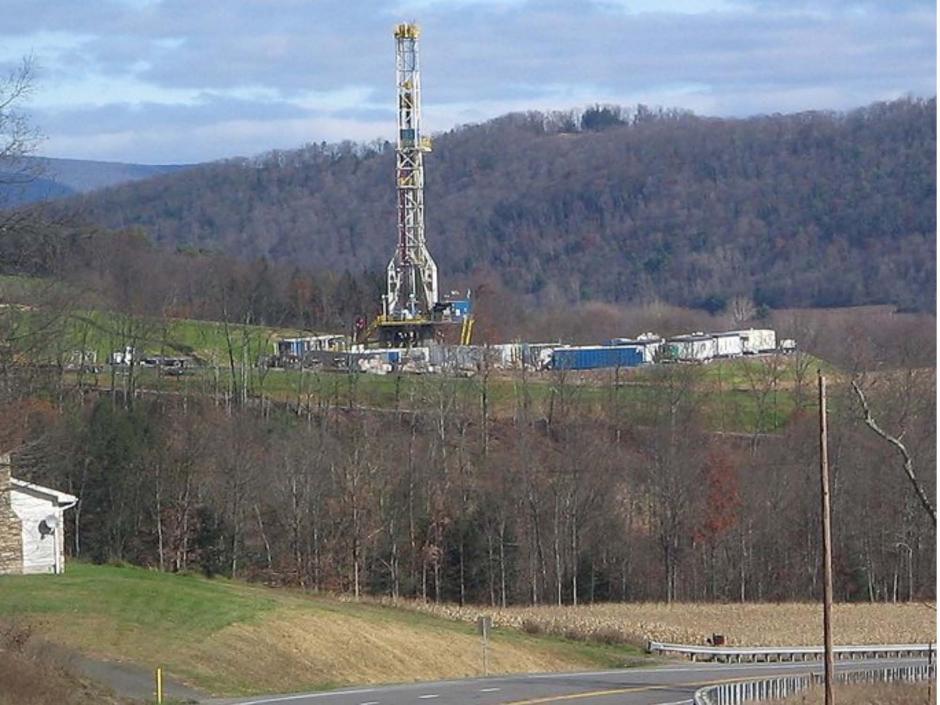

America has received a gift whose consequence and magnitude is just now unfolding before our eyes. Taken to its limits, it may in the course of the next decade finally free us from many of our foreign entanglements while lifting the economic burdens from the working majority that has seen their wages stagnate for the past 40 years.… Read More

Ever since the TSMC OIP Forum where Dr. Shang-Yi Chiang openly asked customers, “When do you want 3D Transistors (FinFETS)?” I have heard quite a few debates on the topic inside the top fabless semiconductor companies. The bottom line, in my expert opinion, is that TSMC will add FinFETS to the N20 (20nm) process node in parallel with… Read More

One of the interesting tidbits of information to come from Intel’s October earnings call was that Brazil, a country of nearly 200M people, has moved up to the #3 position in terms of PC unit sales. This was a shock to most people and as usual brushed aside by those not familiar with the happenings of the emerging markets (i.e. the countries… Read More

The semiconductor design and manufacturing challenges at 40nm and 28nm are a direct result ofMoore’s Law, the climbing transistor count and shrinking geometries. It’s a process AND design issue and the interaction is at the transistor level. Transistors may be shrinking, but atoms aren’t. So now it actually matters when even… Read More

“What would you like your legacy to the world to be? Anything but Moore’s Law!”

Gordon Moore, May 2008.

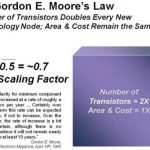

Moore slightly altered the formulation of the law over time, bolstering the perceived accuracy of Moore’s law in retrospect. Most notably, in 1975, Moore altered his projection to a doubling every two years. Despite popular… Read More

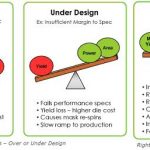

Transistors may be shrinking but atoms are not. Transistors are now just a handful of atoms so it matters even more when a couple of those atoms are out of place. Process variations, whether they are statistical, proximity, or otherwise, have got to be thoughtfully accounted for if we are to achieve the low-power, high-performance,… Read More

This blog is a follow-up to my second most viewed page Moore’s Law and 40nm Yield, with a strong recommendation of how to design for yield at the advanced nodes (32/28/22nm) with Verify High-Sigma design technology.

Case in point: Circuit blocks such as complex standard cells or memory bit cells are repeated thousands or even millions… Read More