Last week TSMC announced the availability of its complete 5nm design infrastructure that enables SoC designers to implement advanced mobile and high-performance computing applications for the emerging 5G and AI driven markets. This fifth generation 3D FinFET design infrastructure includes technology files, PDKs (Process… Read More

Tag: mentor

Functional Verification using Formal on Million Gate Designs

Verification engineers are the unsung heroes making sure that our smart phone chips, smart watches and even smart cars function logically, without bugs or unintended behavior. Hidden bugs are important to uncover, but what approach is best suited for this challenge?

With the Universal Verification Methodology (UVM) there’s… Read More

Hierarchical RTL Based ATPG for an ARM A75 Based SOC

Two central concepts have led to the growth of our ability to manage and implement larger and larger designs: hierarchy and higher levels of abstraction. Without these two approaches the enormous designs we are seeing in SOCs would not be possible. Hierarchy in particular allows the reuse of component blocks, such as CPU cores.… Read More

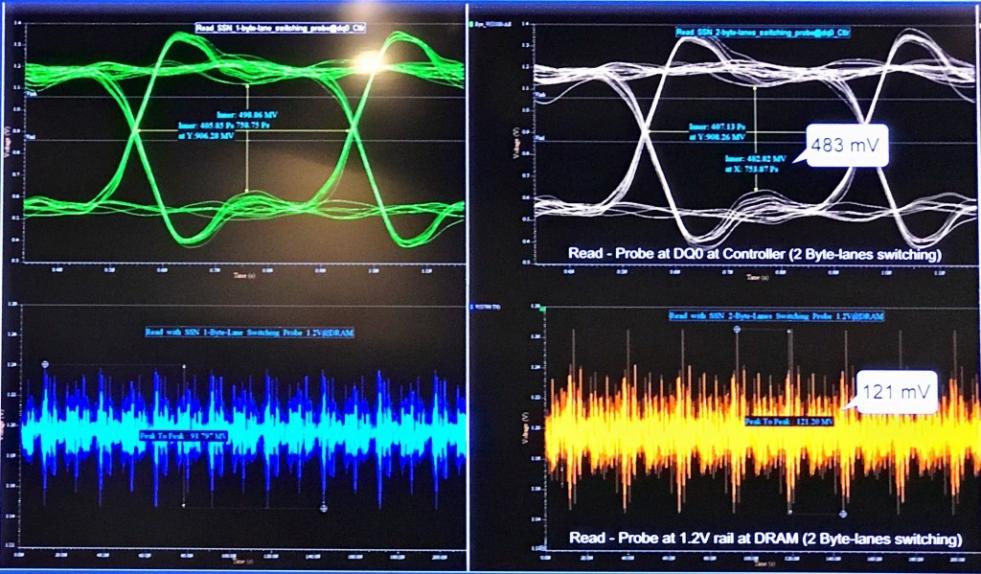

Mentor Automating Design Compliance with Power-Aware Simulation HyperLynx and Xpedition Flow

High-speed design requires addressing signal integrity (SI) and power integrity (PI) challenges. Power integrity has a frequency component. The Power Distribution Network (PDN) in designs has 2 different purposes: providing power to the chip, and acting as a power plane reference for transmission-line like propagating … Read More

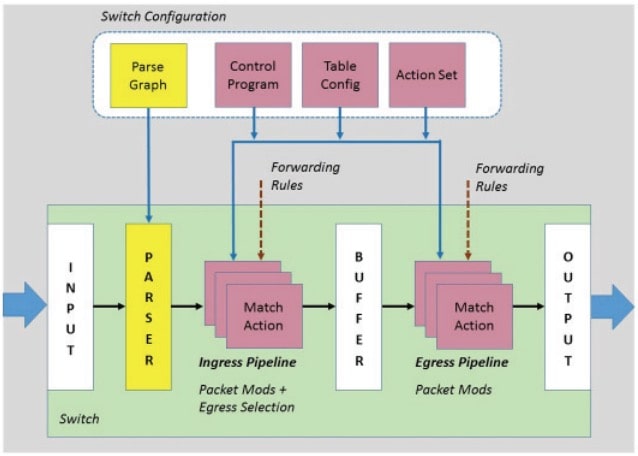

Verifying Software Defined Networking

I’ve designed hardware and written software for decades now, so it comes as no surprise to see industry trends like Software Defined Radio (SDR) and Software Defined Networking (SDN) growing in importance. Instead of designing a switch with fixed logic you can use an SDN approach to allow for greatest flexibility, even … Read More

Accelerating Post-Silicon Debug and Test

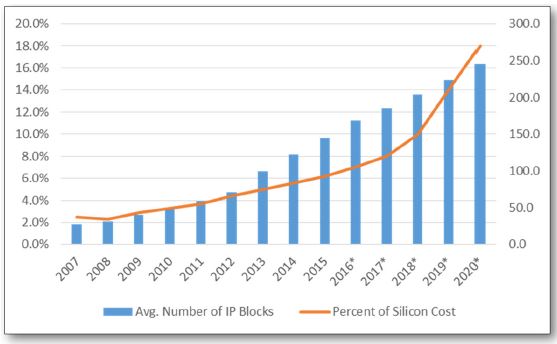

The recent growing complexity in SoC designs attributed to the increased use of embedded IP’s for more design functionalities, has imposed a pressing challenge to the post-silicon bring-up process and impacting the overall product time-to-market.

According to data from Semico Research, more than 60% of design starts contain… Read More

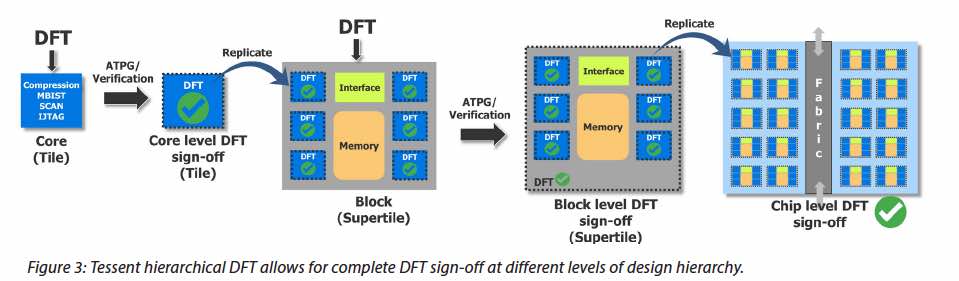

How to be Smart About DFT for AI Chips

We have entered the age of AI specific processors, where specialized silicon is being produced to tackle the compute needs of AI. Whether they use GPUs, embedded programmable logic or specialized CPUs, many AI chips are based on parallel processing. This makes sense because of the parallel nature of AI computing. As a result, in… Read More

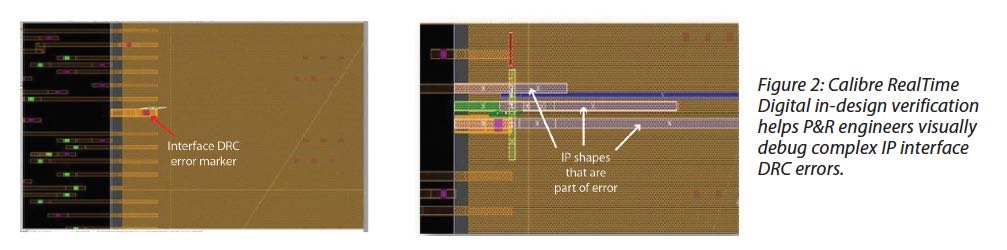

Qualcomm Attests Benefits of Mentor’s RealTime DRC for P&R

When floor planning (FP) and place & route (P&R) tools took over from custom layout tools for standard cell based designs, life became a lot better for designers of large digital chips. The beauty of the new flows was that all the internals of the standard cells and many IP blocks were hidden from view, lightening the load … Read More

Applying Generative Design to Automotive Electrical Systems

Scanning headlines of technology news every day I was somewhat familiar with the phrase “Generative Design” and even browsed the Wikipedia page to find this informative flow-chart that shows the practice of generative design.

Generative design is an iterative design process that involves a program that will generate… Read More

Specialized AI Processor IP Design with HLS

Intelligence as in the term artificial intelligence (AI) involves learning or training, depending on which perspective it is viewed from –and it has many nuances. As the basis of most deep learning methods, neural network based learning algorithms have gained usage traction, when it was shown that training with deep neural network… Read More