You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

EDA companies and foundries must closely collaborate in order to deliver IC tool flows that work without surprises at the 40nm and 28nm nodes.

Tomorrow in San Jose you can attend this 4th annual event hosted by TSMC along with Mentor Graphics and other EDA and IP companies.

Here are some of the topics that will interest IC designers… Read More

Will Rogers said that an economist’s guess is liable to be as good as anyone’s, but with advanced-node optical lithography, I might have to disagree. Unlike the fickle economy, the distorting effects of the mask and lithographic system are ruled by physics, and so can be modeled.

In this installment, I’ll talk about two critical… Read More

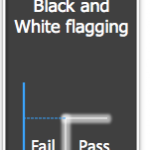

Last week GLOBALFOUNDRIES and Mentor Graphics presented at the Tech Design Forum on how they collaborated on a third generation DFM flow. When I reviewed the slides of the presentation it really struck me on how the old thinking in DRC (Design Rule Checking) of Pass/Fail for layout rules had been replaced with a score represented… Read More

Introduction

Mentor Graphics and GLOBALFOUNDRIES have been working together for several generations since the 65nm node on making IC designs yield higher. Michael Buehler-Garcia, director of Calibre Design SolutionsMarketing at Mentor Graphics spoke with me by phone today to explain how they are working with GLOBALFOUNDRIES… Read More

Wyatt Earp probably wasn’t thinking of OPC when he said, “Fast is fine, but accuracy is everything,” but I’ll adopt that motto for this discussion of full-chip OPC and post-OPC verification models.

Accuracy is the difference between the calibrated model prediction and the calibration wafer result. Accuracy depends on several… Read More

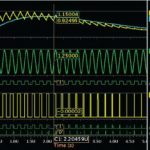

Workshops are a great where to learn hands-on about IC design technology. Mentor has a free workshop to introduce you to creating, simulating and verifying mixed-signal (Analog and Digital) designs.

PLL waveforms showing both digital and analog signals.

Dates in Fremont, California

July 26, 2011

September 15, 2011

November… Read More

Introduction

Before DAC I met with Stephen Pateras, Ph.D. at Mentor Graphics, he is the Product Marketing Director in the Silicon Test Solutions group. Stephen has been at Mentor for two years and was part of the LogicVision acquisition. He was in early at LogicVision and went through their IPO, before that he was at IBM in the mainframe… Read More

Reading the title you guessed it right, Mentor Graphics has three new board members today from the slate offered by billionaire activist Carl Icahn:

- José Maria Alapont, chief executive of the auto parts maker Federal-Mogul

- Gary Meyers, a director of the chip maker Exar

- David Schechter, an executive at Mr. Icahn’s investment firm

…

Read More

Mentor 2 : Carl Icahn 0by Daniel Nenni on 05-01-2011 at 9:46 amCategories: EDA

The corporate raiders are still throwing rocks at Mentor Graphics. I have followed this reality show VERY closely and find their latest assault seriously counterproductive. Disinformation is common in EDA but I expected more from Carl Icahn and the Raiderettes. They are quite the drama queens. Here is a billion dollar question:… Read More

Introduction

Circuit designers work at the transistor level and strive to get the ultimate in performance, layout density or low power by creating crafty circuit topologies in both schematics and layout. Along with this quest comes the daunting task of verifying that all of your rules and best practices about reliability have… Read More