At the recent DesignCon 2019 in Santa Clara, I attended a couple of sessions where Cadence and their research partners provided some insight on machine learning/AI and on large system design analysis; with the first one focused on real-world cloud & machine learning/AI deployment for hardware design and the second one focused… Read More

Tag: machine learning

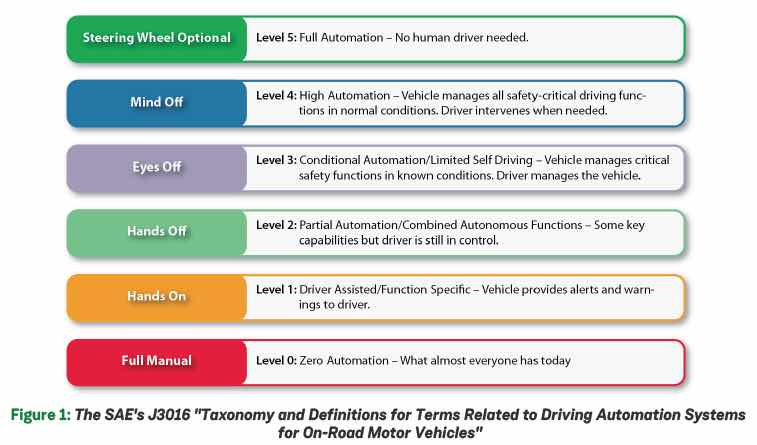

Building Better ADAS SOCs

Ever since we replaced horses in our personal transportation system, folks have been pining for cars that offer some relief from the constant need for supervision, control and management. Indeed, despite their obvious downsides, horses could be counted on to help with steering and obstacle avoidance. There are even cases when… Read More

Improving Library Characterization with Machine Learning!

For SOC designers that are waiting for library models the saying “give me liberty or give me death” is especially apropos. Without libraries to support the timing flow, SOC design progress can grind to a halt. As is often the case, more than just a few PVT corners are needed. Years ago, corners were what the term sounded like – the 4 corners… Read More

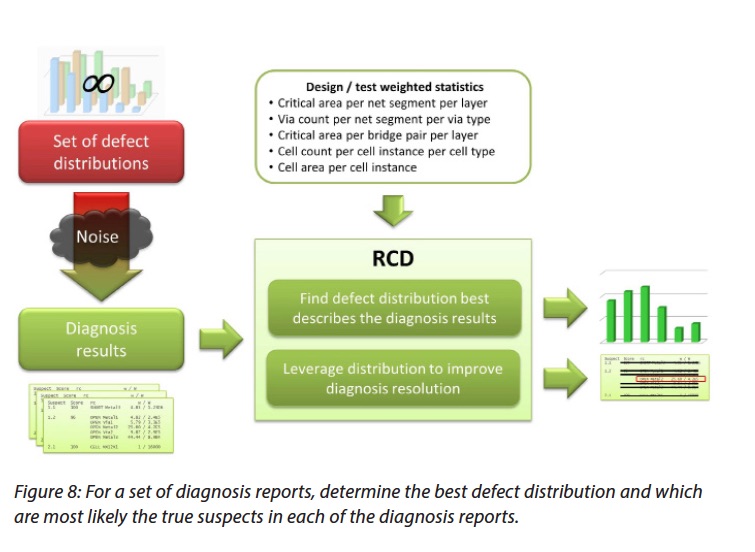

Machine Learning Meets Scan Diagnosis for Improved Yield Analysis

Naturally, chips that fail test are a curse, however with the advent of Scan Logic Diagnosis these failures can become a blessing in disguise. Through this technique information gleaned from multiple tester runs can help pin down the locations of defects. Initially tools that did Scan Logic Diagnosis relied on the netlist to filter… Read More

Cadence Selected to Support Major DARPA Program

When DARPA plans programs, they’re known for going big – really big. Which is what they are doing again with their Electronics Resurgence Initiative (ERI). Abstracting from their intro, this is a program “to ensure far-reaching improvements in electronics performance well beyond the limits of traditional scaling”. This isn’t… Read More

Machine Learning and Embedded FPGA IP

Machine learning-based applications have become prevalent across consumer, medical, and automotive markets. Still, the underlying architecture(s) and implementations are evolving rapidly, to best fit the throughput, latency, and power efficiency requirements of an ever increasing application space. Although ML is … Read More

Cadence’s Smarter and Faster Verification in the Era of Machine Learning, AI, and Big Data Analytics Panel

I attended on Monday, June 25, DAC’s Opening Day, a Cadence-sponsored Lunch panel. Ann Steffora Mutschler (Semiconductor Engineering) was the Moderator and the Panelists were Jim Hogan (Vista Ventures), David Lacey (HP Enterprise), Shigeo Oshima (Toshiba Memory Corp), Paul Cunningham (Cadence).… Read More

DAC 2018 Potpourri

The venue

Despite of being held at the new three-story Moscone West building, this year 55th DAC in San Francisco bore many similarities as compared with last year’s. Similar booth decors and floorplan positioning of the big two, Synopsys and Cadence, which were across of each other and right next to the first floor entrance –although… Read More

Machine Learning Drives Transformation of Semiconductor Design

Machine learning is transforming how information processing works and what it can accomplish. The push to design hardware and networks to support machine learning applications is affecting every aspect of the semiconductor industry. In a video recently published by Synopsys, Navraj Nandra, Sr. Director of Marketing, takes… Read More

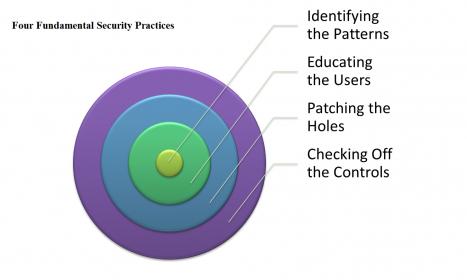

First Line of Defense for Cybersecurity: AI

The year 2017 wasn’t a great year for cyber-security; we saw a large number of high-profile cyber attacks; including Uber, Deloitte, Equifax and the now infamous WannaCry ransomware attack, and 2018 started with a bang too with the hackingof Winter Olympics. The frightening truth about increasingly cyber-attacks is … Read More