On-chip variation (OCV) is a major issue in timing signoff, especially at low voltages or in 20/16/14nm processes. For example, the graph below shows a 20nm inverter. At 0.6V the inverter has a delay of 2 (nominalized) units. But due to on-chip variation this might be as low as 1.5 units or as high as 3 units, which is a difference from… Read More

Tag: low power

Voltage Limbo Dancing: How Low Can You Go?

All chips these days have to worry about power. Indeed it is typically the top of the priority list of concerns, above performance and even area. Transistors are effectively fast and free, but you can’t have too many of them (at least turned on at once). The most obvious way to reduce power is to lower the supply voltage. This … Read More

Components for Wearables, Making the IoT Real

The screenwriter William Goldman is famous for saying that in Hollywood “Nobody knows anything.” Meaning that there is simply no way for any of the people involved to be able to predict which movies will turn out to be hits and which will be flops. I think the internet of things (IoT) is going to be like that. There will … Read More

Processor for Internet-of-Things (IoT)

Due to increasing proliferation of sensors in our everyday lives, evolution of IoT is natural. The mix of different building blocks with different speed-power-performance constraints makes IoT as the hottest upcoming application area for semiconductor IP vendors. The System-on-Chips (SoCs) coming up in this area typically… Read More

Palladium’s Little Brother Protium

Today, Cadence announced Protium, a new FPGA prototyping platform for software development. During development of an SoC, the most appropriate methodology changes. In the early days, developing RTL, the primary tool is simulation. Then, as the blocks get bigger or as the whole chip starts to come together, typically simulation… Read More

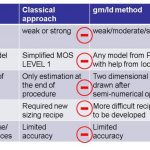

Keywords: FD-SOI, Cost, FinFET

How to synthesize a pretty good article Is SOI Really Less Expensive, and even more important the impressive amount of comments (56) generated? Let’s start with the initial article. Pretty good, but slightly biased, when you carefully dissect it, like I did in one of the comments (you can find it in-extenso at the end of this post).… Read More

Sensor Hub and Wearable Gestures

One of the challenges with the internet of things (IoT) is that many devices are both always on and battery powered (and not with a large battery). The responsibilities need to be split so that the device senses when it needs to wake up without requiring the application processor to be waking up all the time to make the decision since… Read More

Full-Custom Low Power Design Methodology

Digital designers have used logic optimization and logic synthesis for decades as a means to produce more optimal designs with EDA tools. On the analog and transistor-level side of design the efforts to automatically optimize for speed or power have generally been limited to circuits with only a handful of transistors. These … Read More

Low Power Design

So you want to do a low power design. Join the club. Who doesn’t? Today all designs are low power, it is the biggest constraint on what we can do on a chip. Power down; power domains, variable clock rates, mixed Vt libraries. Every trick is needed. And that is not even enough. We get to put our phones on charge each evening and there… Read More

Intel Quark awakening from stasis on a yet-to-be-named planet

We know the science fiction plot device from its numerous uses: in order to survive a journey of bazillions of miles across galaxies into the unknown future, astronauts are placed into cryogenic stasis. Literally frozen in time, the idea is they exit a lengthy suspension without aging, ready to go to work immediately on revival … Read More