Major power reductions are possible by reducing power at the RTL and system levels, and not just at the gate and physical level. In fact, as is so often the case in design, changes can have much more impact when done at the higher level, even given that at that point in the design there is less accurate feedback about changes. Later the… Read More

Tag: low power

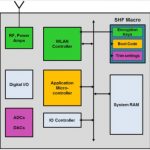

Using OTP Memories To Keep SoC Power Down

Virtually all SoCs require one-time programmable (OTP) memory. Each SoC is different, of course, but two main uses are large memories for holding boot and programming code and small memories for holding encryption keys and trimming parameters, such as radio tuning information and so on.

There are alternatives to putting an OTP… Read More

Xilinx At 28nm: Keeping Power Down

Almost without exception these days, semiconductor products face strict power and thermal budgets. Of course there are many issues with dynamic power but one big area that has been getting increasingly problematic is static power. For various technical reasons we can no longer reduce the voltage as much as we would like from one… Read More

RTL Design For Power

My Samsung Galaxy Note II lasts about two days on a single battery charge, which is quite the improvement from the Galaxy Note I with only a one day battery charge. Mobile SoCs are being constrained by battery life limitations, and consumers love longer-laster devices.

There are at least two approaches to Design For Power:

- Gate-level

Challenges of Low Power Network-on-Chip Designs

Everyone understands that as we increasingly focus on the design of mobile devices, there is an increasing focus on low power. But, what is implied in designing for low-power? Designing for low power means we have to work with multiple power domains and multiple clock domains—making our design task more complex. We also must get… Read More

Qualcomm Video Friday

Two videos (both short) from Qualcomm. They are both amusing but also have a serious aspect to them. The first one is interesting since it is Qualcomm following in Intel’s footsteps with its “Intel Inside” campaign against AMD to make people care about what processor was in their PC. Until that point probably… Read More

Today’s Program is Brought To You by the Letter A

What do nVidia, Freescale and GlobalFoundries have in common? They are semiconductor companies? They are ARM licensees? They are doing 28nm chips? They all have the letter ‘a’ in their names?

All true, but that’s not what I was thinking of. But the letter ‘a’ is a clue since Apache (and Ansys) begin with ‘a’. All three companies have… Read More

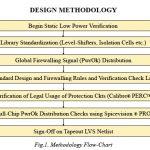

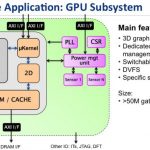

Static Low-Power Verification in Mixed-Signal SoC Designs

IC designer Shubhyant Chaturvediof AMD used EDA tools from Mentor Graphicsand Concept Engineeringto perform static, low-power verification of a mixed-signal SoC design with a combined CPU and GPU. Shubhyant presented a poster session at DAC two weeks ago in Austin, and I wanted to share it with my readers here at SemiWiki.… Read More

Interview with Forte CTO John Sanguinetti on Cynthesizer 5

Recently, Forte Design Systems announced the release of a new core engine to their popular high-level synthesis tool offering. It is a large undertaking, so I asked John Sanguinetti, Forte’s CTO, to answer some questions about that development effort.

Q. How long has it been since the last major upgrade of the Cynthesizer… Read More

Jasper Low Power Verification App

Today, Jasper announced their new Jasper-Gold Low Power Verification App. This is focused on verifying low power designs with multiple power domains, voltage islands, power shutoff, clock shutoff, and all the other techniques used for reducing power. Of course power is the main driver of SoC design these days, whether it is for… Read More