You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

While tracking Moore’s Law has become a more expensive and difficult endeavor in the HPC design, the mobile SOC design space is also increasingly heterogeneous and complex. Strict safety guidelines such as the ISO-26262 being imposed in the automotive applications further exacerbate the situation.

Looking closer into the … Read More

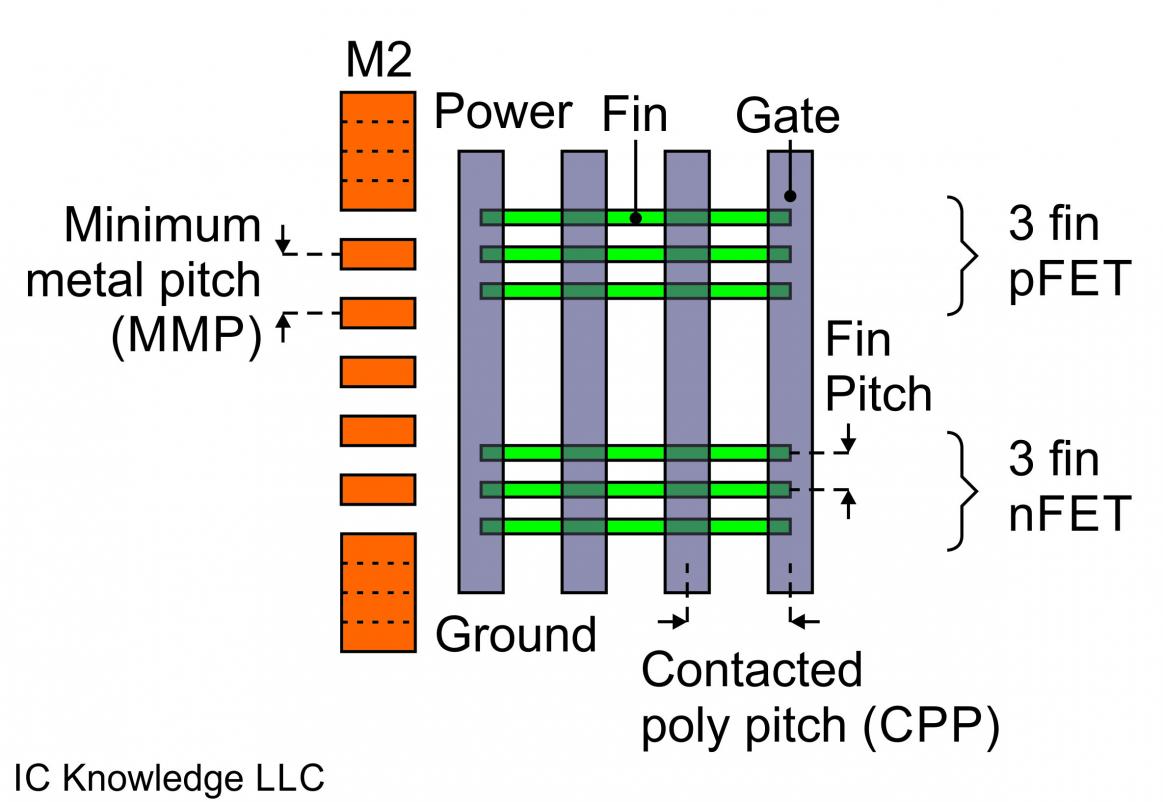

I was invited to give a talk at the Business of Cleans Conference held by Linx Consulting in Boston on April 9th. I am not a cleans expert but rather was invited more to give an overview talk on process technology trends and the impact on cleans. In this write up I will discuss my presentation. I discussed each of the three main leading-edge… Read More

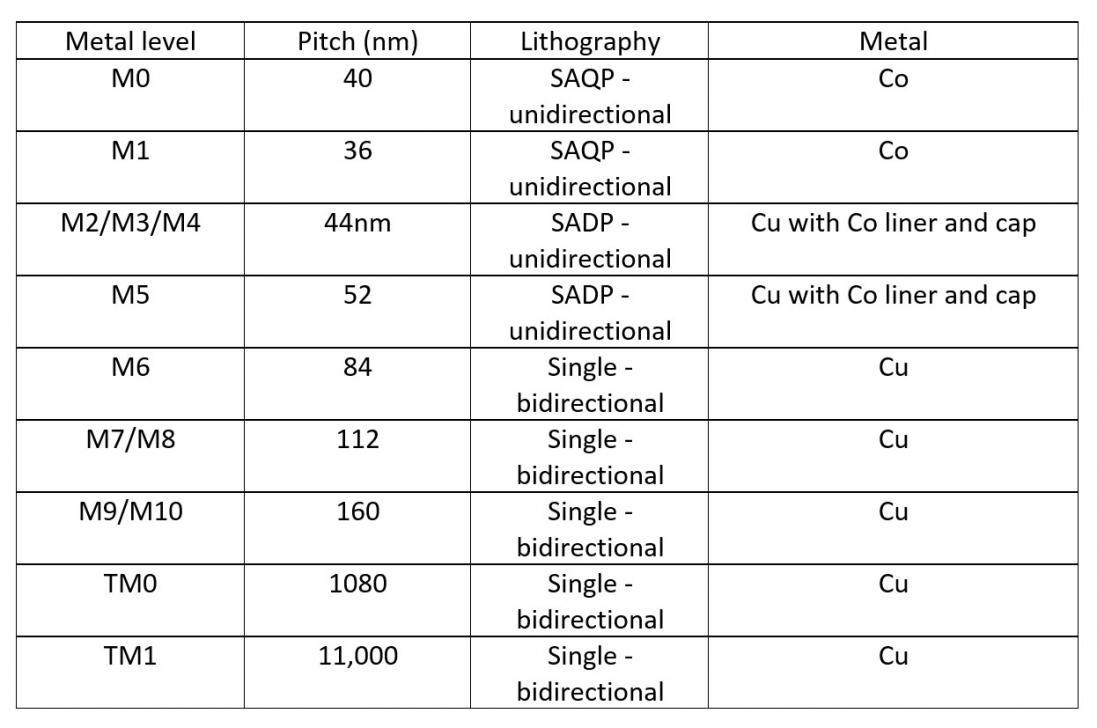

The most viewed blogs I write for SemiWiki are consistently blogs comparing the four leading edge logic producers, GLOBALFOUNDRIES (GF), Intel, Samsung (SS) and TSMC. Since the last time I compared the leading edge new data has become available and several new processes have been introduced. In this blog I will update the current… Read More

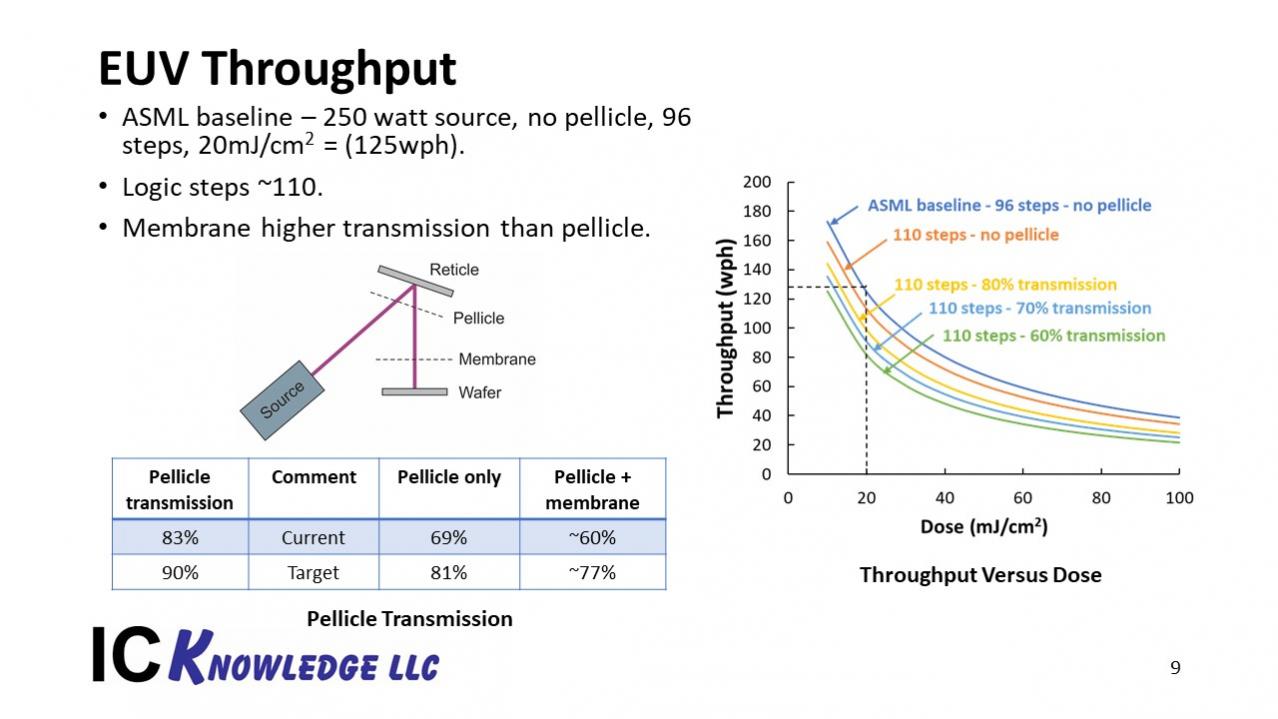

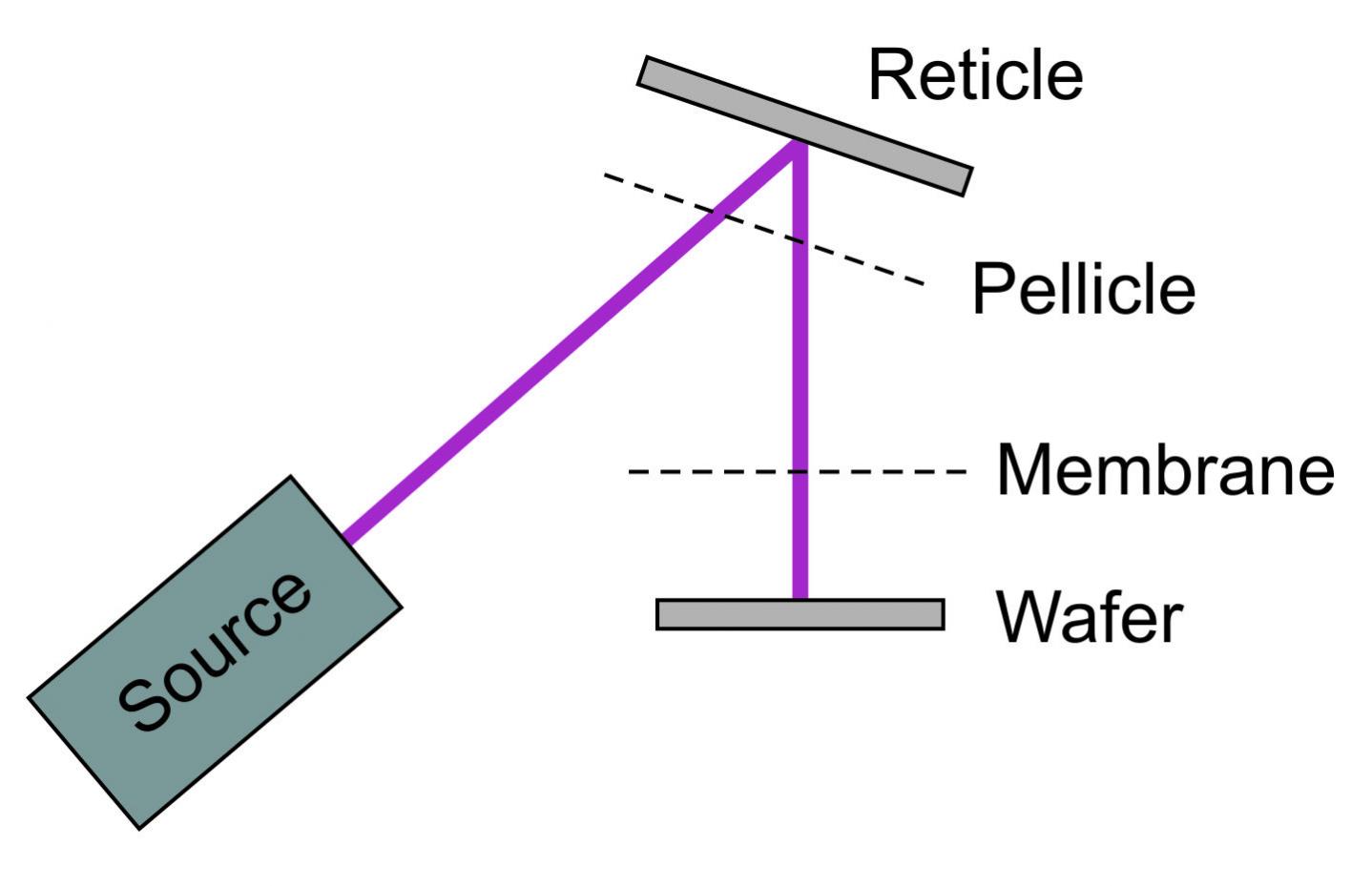

This year the Advanced Lithography Conference felt very different to me than the last couple of years. I think it was Chris Mack who proclaimed it the year of Stochastics. EUV has dominated the conference for the last several years but in the past the conversation has been mostly centered on the systems, system power and uptime.

I … Read More

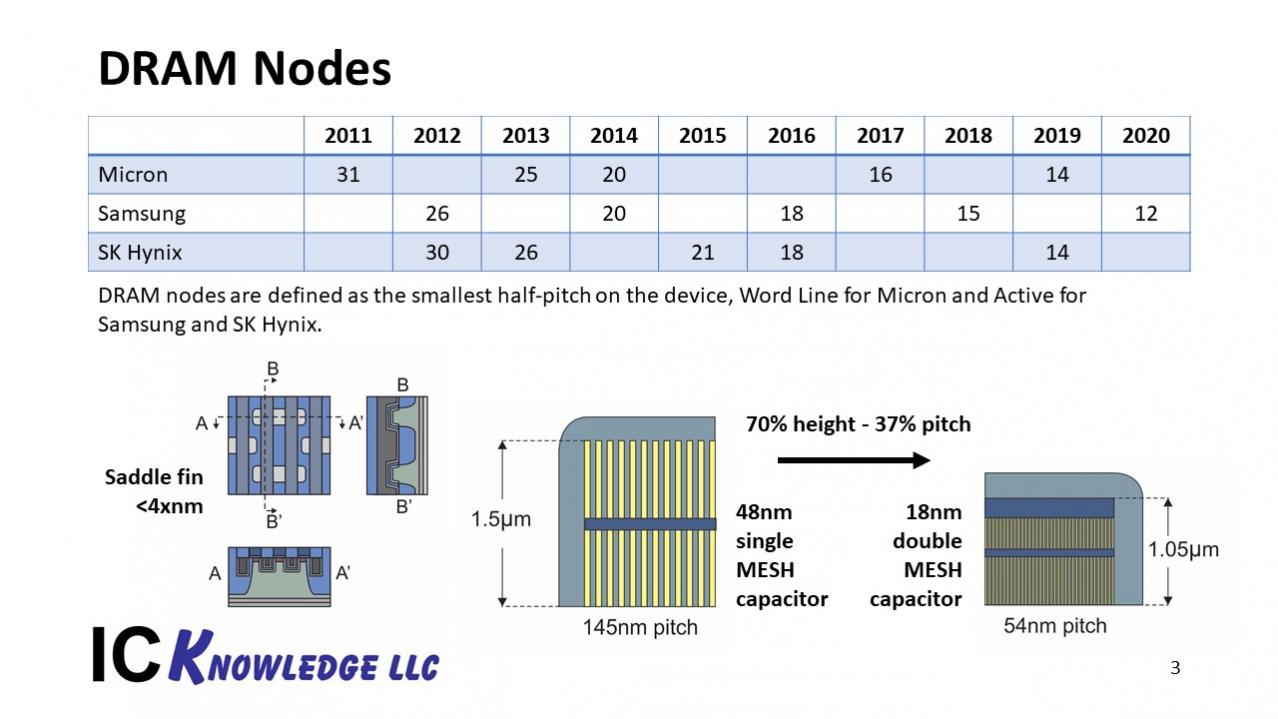

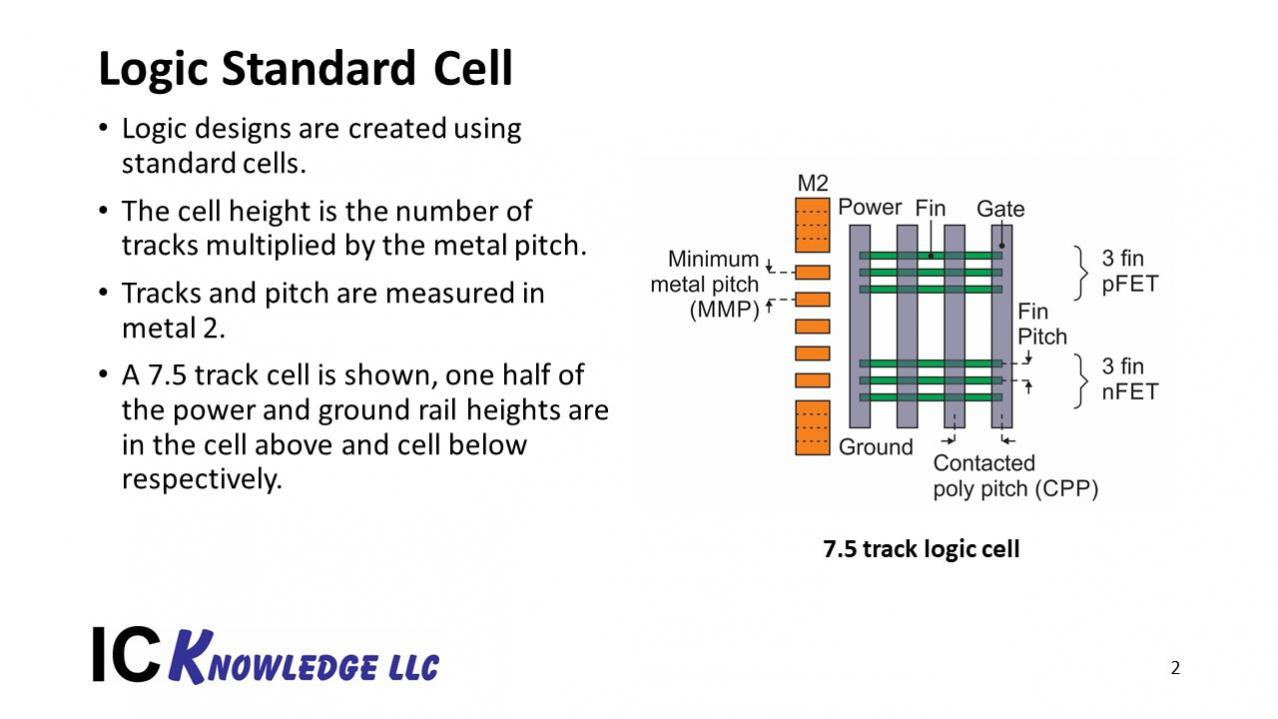

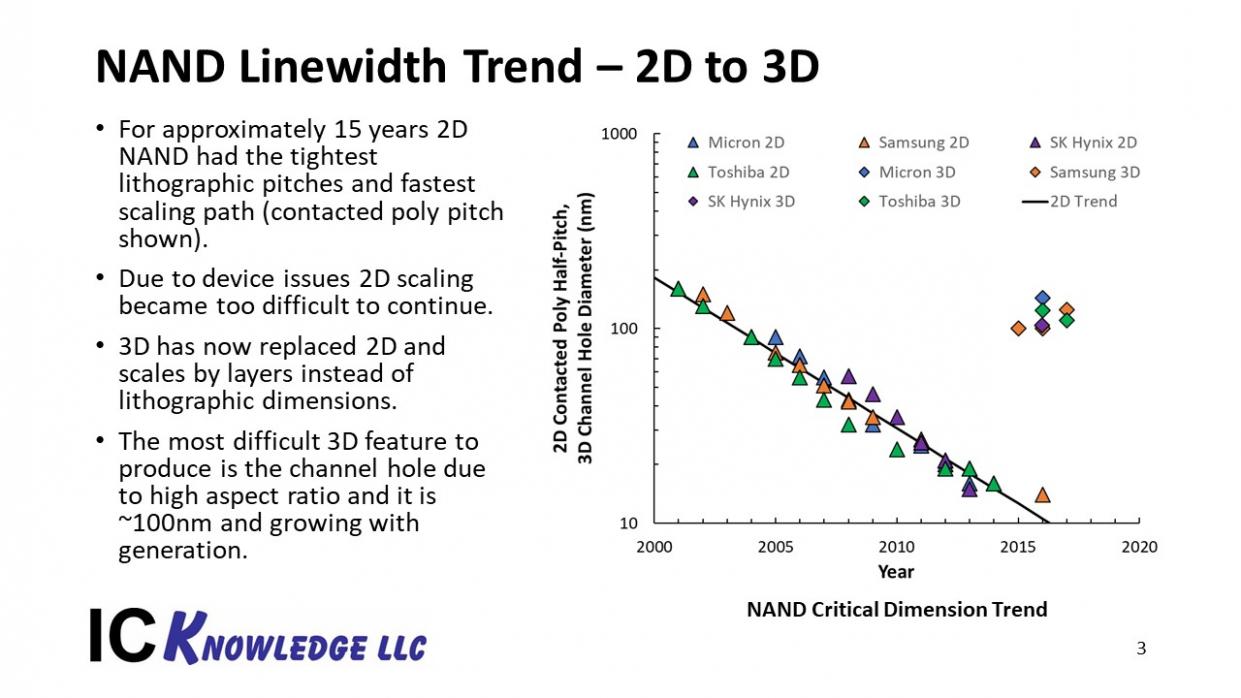

I was invited to present at Nikon’s LithoVision event held the day before the SPIE Advanced Lithography Conference in San Jose. The following is a write up of the talk I gave. In this talk I discuss the three main segments in the semiconductor industry, NAND, DRAM and Logic and how technology transitions will affect lithography.… Read More

At IEDM in December I had a chance to interview Thomas Ernst about the paper “Performance and Design Considerations for Gate-All-around Stacked-NanoWires FETs” by Leti and STMicroelectonics.

Leti published the first stacked nanowire in 2006, it was very new then, now stacked nanowire/nanosheets are starting… Read More

As I have said many times, IEDM is one of the premier conferences for semiconductor technology. On Sunday before the formal conference started I took the “Boosting Performance, Ensuring Reliability, Managing Variation in sub-5nm CMOS” short course. The second module in the course was “Multi-Vt Engineering… Read More

I was invited to give a talk at the ISS conference on the Impact of EUV on the Semiconductor Supply Chain. The ISS conference is an annual gathering of semiconductor executives to review technology and global trends. In this article I will walk through my presentation and conclusions.… Read More

As I have discussed in previous blogs, IEDM is one of the premier conferences to learn about the latest developments in semiconductor technology. … Read More

The challenges of 7nm are well documented. Lithography artifacts create exploding design rule complexity, mask costs and cycle time. Noise and crosstalk get harder to deal with, as does timing closure. The types of applications that demand 7nm performance will often introduce HBM memory stacks and 2.5D packaging, and that creates… Read More