This is the 15th anniversary of the TSMC Open Innovation Platform (OIP). The OIP Ecosystem Forum will kick off on September 27th in Santa Clara, California and continue around the world for the next two months in person and on-line in North America, Europe, China, Japan, Taiwan, and Israel. These are THE most attended semiconductor… Read More

Tag: gdsii

Honey I Shrunk the EDA TAM

The “20 Questions with Wally Rhines” series continues

Throughout the history of the EDA industry, pricing models have caused discontinuities in the way the industry operates. For a variety of competitive reasons, individual companies have developed ways to change the pricing model in an attempt to secure competitive… Read More

Is there anything in VLSI layout other than “pushing polygons”? (3)

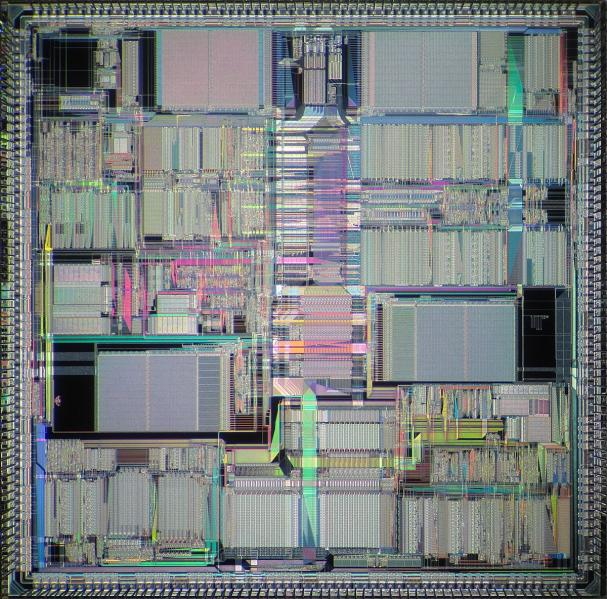

In late 1986 the Layout Project Leader of DSP96000 got married and left for a 6 months’ vacation so I inherited the biggest chip MSIL had in stock. Floorplanning such size chip was a challenge from day one. Even the 68030 SUN workstation was too slow. I started to ask around and going to demos for any other possible tool that can help me… Read More

Is there anything in VLSI layout other than pushing polygons? (2)

One of the important changes that happen between 1984 and 1988 is the hardware platforms development. Calma evolved, mainframe S140 with 2 combined monitors per terminal in S280 with 2 individual monitors per terminal. This meant that from noisy and darker rooms we move to more quiet and lighted rooms. We doubled the speed and the… Read More

Why Open and Supported Interfaces Matter

Back in the early 1980’s during the nascent years of electronic design automation (EDA), I worked at Texas Instruments supporting what would become their merchant ASIC business. Back then, life was a bit different. The challenge we faced was to make our ASIC library available on as many EDA flows as we could to give as many users as… Read More

Business Models: EDA Is Software But It Used To Be Sold As Hardware

Business models are really important. Just ask any internet startup company that has lots of eyeballs and is trying to work out how to monetize them. It is a lot easier to get people to use something for free, much harder to get people to pay for something especially when they don’t value it much. Different companies that look… Read More

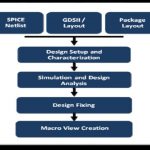

eSilicon Creates One-Click Access to MPW and GDSII Quoting Portals

I have written before about eSilicon taking their internal quoting tool and making it user accessible. This first started just for MPW shuttles for half-a-dozen foundries, and then was extended to cover production runs at TSMC. And it is getting heavily used; eSilicon have had 315 people register to use it from 43 different countries… Read More

Xilinx & Apache Team up for FPGA Reliability at 20nm

In this age of SoCs with hundreds of IPs from different sources integrated together and working at high operating frequencies, FPGA designers are hard pressed keeping up the chip reliability from issues arising out of excessive static & dynamic IR drop, power & ground noise, electro migration and so on. While the IPs are… Read More

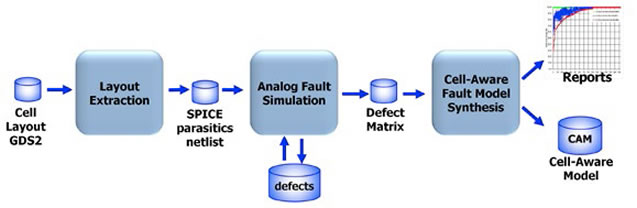

Patterns looking inside, not just between, logic cells

Traditional logic testing relies on blasting pattern after pattern at the inputs, trying to exercise combinations to shake faults out of logic and hopefully have them manifested at an observable pin, be it a test point or a final output stage. It’s a remarkably inefficient process with a lot of randomness and luck involved.

Getting… Read More

Robust Design <- Robust Flow <- Robust Tools

I could have written the sequence of the title in reverse order, but no, design is the one which initiates the need of a particular flow and the flow needs support of EDA tools to satisfy that need. It’s okay if the design is small; some manual procedures and workarounds/scripts may be able to perform certain jobs. However, as the design… Read More