You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

If you plan on visiting Solido (the world leader in EDA software for variation-aware design of integrated circuits) at the Design Automation Conference next month for a demonstration of Variation Designer, register online now and get an autographed copy of “Mobile Unleashed”. Such a deal!

Solido Variation Designer is used by… Read More

Being that TSMC and Solido are founding members of SemiWiki, you should be able find out everything you ever wanted to know on their respective landing pages. If not, just ask a question in the SemiWiki forum and I can assure you it will be answered in great detail. And here are some other interesting 2015 factoids from Solido:… Read More

We in Semiwiki are writing about FD-SOI since 2012, describing all the benefits offered by the technology in term of power consumption, price per performance compared with FinFET, etc. Let me assess again that I am fully convinced that FD-SOI is a very smart and efficient way to escape from the Moore’s law paradox: the transistor… Read More

At SemiWiki we’ve been blogging for several years now on the semiconductor design challenges of FinFET technology and how it requires new software approaches to help chip designers answer fundamental questions about timing, power, area and design closure. When you mention the phrase Static Timing Analysis (STA) probably… Read More

According to the IEEE Std 1012-2012, verification is the acknowledgement that a product is in satisfactory condition by meeting a set of rigorous criteria. [3] Transistor-level verification involves the use of custom libraries and design models to achieve ultimate performance, low power, or layout density. [2] Prediction… Read More

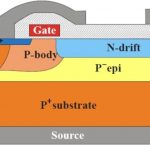

Process and device engineers are some of the unsung heroes in our semiconductor industry that have the daunting task of figuring out how to actually create a new process node that will fit some specific, market niche with sufficient yield to make their companies profitable and stand out from the competition. One such market segment… Read More

The intricacies of analog IP circuit design have always required special consideration during physical layout. The need for optimum device and/or cell matching on critical circuit topologies necessitates unique layout styles. The complex lithographic design rules of current FinFET process nodes impose additional restrictions… Read More

Evolving opportunities call for new and improved solutions to handle data, bandwidth and power. Moving forward, what will be the high-growth applications that drive product and technology innovation? The CAGRs for smartphone and data center continue to be very strong and healthy. … Read More

It seems of late like there is an unlimited thirst for GPU performance at the right power efficiency. Whether it is deep learning, object recognition, artificial intelligence, simulations, VR or AR, the industry desperately needs GPU improvements. Many within the graphics industry would agree that a new era of graphics performance… Read More

The growth of mobile and IoT have helped increase the demand for One Time Programmable Non Volatile Memory (OTP NVM) as a solution for on-chip storage. To continue to meet this demand and grow with it, industry leading Sidense has recently brought on board seasoned semiconductor executive Ken Wagner as VP of Engineering. He was … Read More