During the 1940s when aerospace engineers were attempting to break the sound barrier for the first time, they were confronting a slew of new technical issues that had never been dealt with before, and in some cases never seen before. In subsonic flight airflow was predictable and well understood. In crossing the sound barrier, … Read More

Tag: esilicon

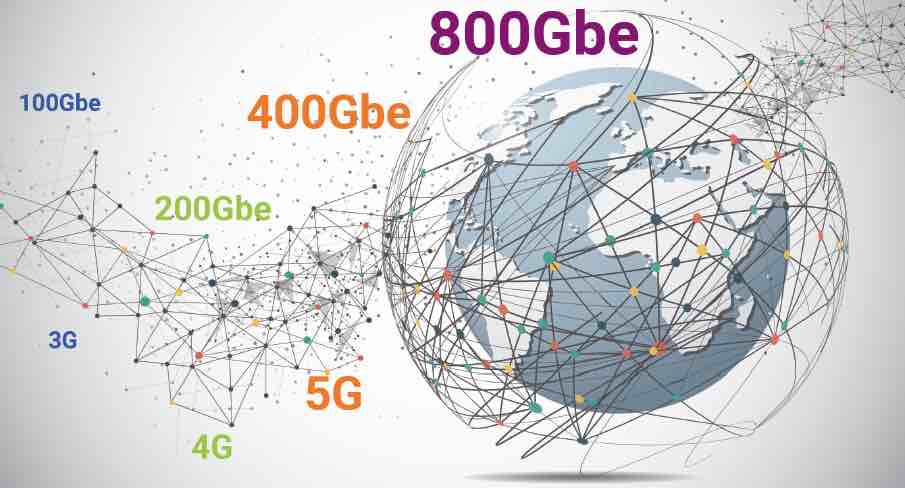

56G and 112G SerDes Where the rubber meets the road

No matter how high the processing capability of a chip, its overall performance is limited by IO speed. This is very similar to a car with low performance tires, a powerful engine will not be able to transfer its energy to the ground effectively. There is quite literally a race going on between core processing and IO speeds for transferring… Read More

Playing the Long Game with 56G SerDes

IP has always been a hot topic on SemiWiki with quite a bit of our readers doing the “make versus buy” analysis. SerDes is one of the more difficult “makes” so it is mostly a “buy” analysis made by networking class ASIC architects and a handful of other applications that demand high performance and throughput. Based on the recent traffic… Read More

The Ever-Changing ASIC Business

The cell-based ASIC business that we know today was born in the early 1980s and was pioneered by companies like LSI Logic and VLSI Technology. Some of this history is covered in Chapter 2 of our book, “Fabless: The Transformation of the Semiconductor Industry”. The ASIC business truly changed the world. Prior to this revolution,… Read More

Measuring Up 7nm IP

The Linley Group is an industry-leading source for independent technology analysis of semiconductors for networking, communications, mobile, and data-center applications. Their Microprocessor Report is widely read as a source of un-biased, no-nonsense analysis of technologies and trends. So, when they dig into something… Read More

eSilicon and SiFive partner for Next-Generation SerDes IP

While writing “Mobile Unleashed: The Origin and Evolution of ARM Processors In Our Devices” it was very clear to me that ARM was an IP phenomenon that I did not believe would ever be repeated. Clearly I was wrong as we now have RISC-V with an incredible adoption rate, a full fledged ecosystem, and top tier implementers… Read More

7nm Networking Platform Delivers Data Center ASICs

We all know IP is critical for advanced ASIC design. Well-designed and carefully tested IP blocks and subsystems are the lifeblood of any advanced chip project. Those IP suppliers who can measure up to the need, especially at advanced process nodes, will do well, absolutely.

It is interesting to note that eSilicon now has a very … Read More

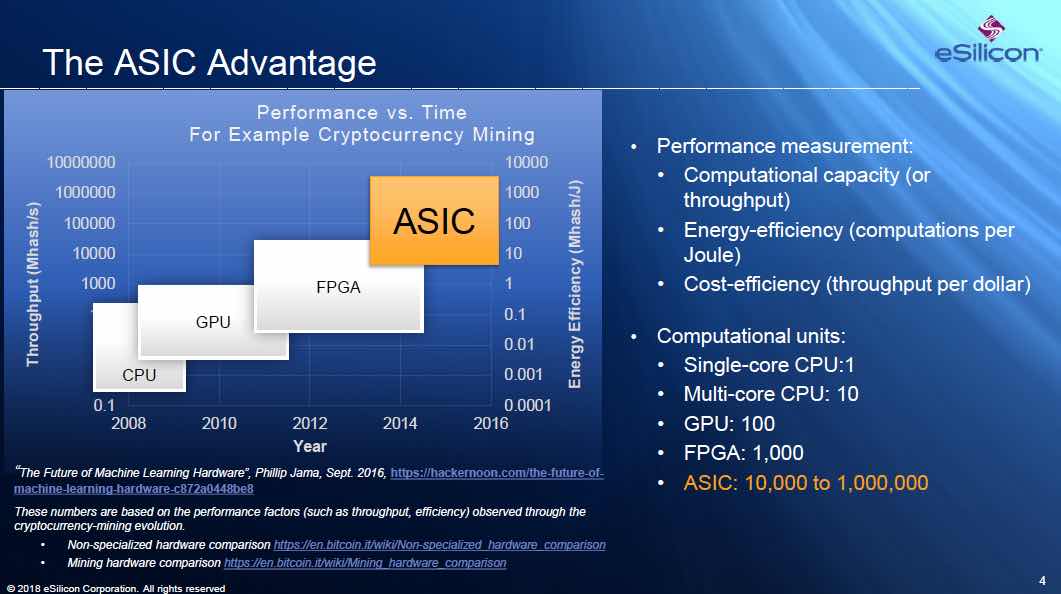

Being Intelligent about AI ASICs

The progression from CPU to GPU, FPGA and then ASIC affords an increase in throughput and performance, but comes at the price of decreasing flexibility and generality. Like most new areas of endeavor in computing, artificial intelligence (AI) began with implementations based on CPU’s and software. And, as have so many other applications,… Read More

What does a Deep Learning Chip Look Like

There’s been a lot of discussion of late about deep learning technology and its impact on many markets and products. A lot of the technology under discussion is basically hardware implementations of neural networks, a concept that’s been around for a while.

What’s new is the compute power that advanced semiconductor technology… Read More

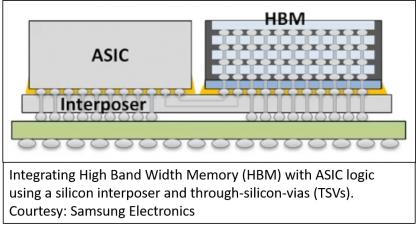

High Performance Ecosystem for 14nm-FinFET ASICs with 2.5D Integrated HBM2 Memory

High Bandwidth Memory (HBM) systems have been successfully used for some time now in the network switching and high-performance computing (HPC) spaces. Now, adding fuel to the HBM fire, there is another market that shares similar system requirements as HPC and that is Artificial Intelligence (AI), especially AI systems doing… Read More