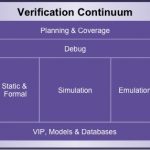

Verification spans a number of different technologies, from virtual platforms, RTL simulation, formal techniques, emulation and FPGA prototyping. Going back a few years, most of these technologies came from separate companies and one effect of this was that moving the design from one verification environment to another required… Read More

Tag: emulation

Vlang – Opportunities Galore for Productivity & Performance

Yes, verification technologies are open to innovation for improved productivity and performance in the face of ever growing SoC/IP design sizes and complexities. There is not much scope left in processor speed to improve, other than multi-core processors in servers which again need software properly architected to be thread-able… Read More

Transaction-based Emulation

Verification has been going through a lot of changes in the last couple of years. Three technologies that used to be largely contained in their own silos have come together: simulation, emulation and virtual-platforms.

Until recently, the workhorse verification tool was simulation. Emulation had its place but limits on capacity… Read More

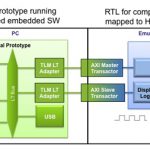

Hybrid Emulation

Hybrid emulation is when part of the system is run in the emulator and part of the system is run in a virtual prototype. Typically a model of the processor(s) is run in the virtual platform and then the rest of the design is modeled by running the RTL on the emulator. I talked to Tom Borgstrom at Synopsys about what technology they have … Read More

Cadence Results: Good but Palladium under Price Pressure

Cadence announced their 2Q results this afternoon. I listened to the conference call.

You can read all the details of the results in the press release but the big picture is:

- Revenue $379K, net income $23M GAAP or $64M non-GAAP (8, 21c per share, beat estimates by 1c). Equivalent quarter last year was $362M so less than 5% increase)

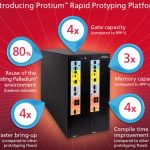

Palladium’s Little Brother Protium

Today, Cadence announced Protium, a new FPGA prototyping platform for software development. During development of an SoC, the most appropriate methodology changes. In the early days, developing RTL, the primary tool is simulation. Then, as the blocks get bigger or as the whole chip starts to come together, typically simulation… Read More

A Brief History of Functional Verification

Usually these brief history pieces are totally written by the SemiWiki blogger whose name is at the top. Often me since that was how I prototyped book chapters (buy). Well, OK, I did actually write this but it is completely cribbed from a presentation earlier this week by Wally Rhines who gave a sort of keynote at the announcement of… Read More

Synopsys Announces Verification Compiler

Integration is often an underrated attribute of good tools, compared to raw performance and technology. But these days integration is differentiation (try telling that to your calculus teacher). Today at DVCon Synopsys announced Verification Compiler which integrates pretty much all of Synopsys’s verification technologies… Read More

Synopsys’s Next Generation Emulator, ZeBu Server-3

Since Synopsys acquired Eve over a year ago, they haven’t announced anything new in the ZeBu product line. Emulators are not like software where you expect incremental releases a couple of times per year, each new “release” is a complete re-design using new hardware fabric in a new process technology. Earlier… Read More

nVidia: Virtual Platform/Emulation Hybrid

I was the VP marketing at VaST Systems Technology and then at Virtutech. Both companies sold virtual platform technology which consisted of two parts:

- an extremely fast processor emulation technology that actually worked by doing a binary translation of the target binary code (e.g. an ARM) into the native instruction set of the