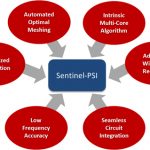

The last of the current series of webinars is on Sentinel-PSI,IC-Package, Power and Signal Integrity Solution. It will be at 11am Pacific time on Thursday 11th August. It will be conducted by Dr. Tao Su, product manager of the Sentinel products. Dr. Su has many years of experience in the EDA industry and is specialized in power integrity… Read More

Tag: eda

August 11th – Hands-on Workshop with Calibre: DRC, LVS, DFM, xRC, ERC

I’ve blogged about the Calibre family of IC design tools before:

Smart Fill replaced Dummy Fill Approach in a DFM Flow

DRC Wiki

Graphical DRC vs Text-based DRC

Getting Real time Calibre DRC Results with Custom IC Editing

Transistor-level Electrical Rule Checking

Who Needs a 3D Field Solver for IC Design?

Prevention is Better… Read More

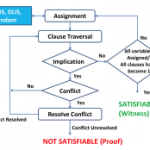

Assertion-based Formal Verification

Formal verification has grown in importance as designs have grown and it has become necessary to face up to the theoretical impossibility of using simulation to get complete coverage along with the practical impossibility of simulating enough to even get close.

There are a number of solvers for what is called satisfiability (SAT)… Read More

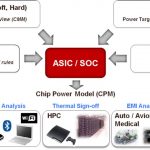

Chip-Package-System Webinar

The webinar on CPS (chip-package-system) is on Tuesday 9th August at 11am Pacific time. It will be conducted by Christopher Ortiz, Principal Application Engineer at Apache Design Solutions. Dr. Ortiz has been with Apache since 2007, supporting the Sentinel product line. Prior to Apache he worked at Agere / LSI, where he investigated… Read More

Smart Fill Replaces Dummy Fill Approach in a DFM Flow

I met with Jeff Wilson, Product Marketing Manager at Mentor in the Calibre product group to learn more about Smart Fill versus Dummy Fill for DFM flows. Jeff works in the Wilsonville, Oregon office and we first meet at Silicon Compilers back in the 1990’s.

Dummy Fill

This diagram shows an IC layout layer on the left as originally… Read More

Totem webinar: Analog/Mixed-Signal Power Noise and Reliability

The Totem webinar will be at 11am on Tuesday 2nd August. This session will be conducted by Karan Sahni, Senior Applications Engineer at Apache Design Solutions. Karan has been with Apache since 2008, supporting the Redhawk, Totem, Sentinel product lines. He received his MS in Electrical Engineering from the Syracuse University… Read More

CDNS EDA360 is DEAD!

Hard to believe EDA360, the Cadence Blueprint toBattle ‘Profitability Gap’; Counters Semiconductor Industry’s Greatest Threat!, is DEAD at the ripe old age of one. As you may have already read John Bruggeman left Cadence after the company conference call last week. The formal announcement should go out on Monday after the SEC… Read More

Global Technology Conference 2011

Competition is what made the semiconductor industry and semiconductors themselves what they are today! Competition is what drives innovation and keeps costs down. Not destructive competition, where the success of one depends on the failure of another, but constructive competition that promotes mutual survival and growth… Read More

PowerArtist webinar

The next Apache webinar is on PowerArtist, RTL Power Analysis on July 26th at 11am Pacific time. The webinar will be conducted by David “Woody” Norwood, Principal Applications Engineer at Apache Design Solutions. David has been supporting RTL Power products for the past 8 years. He has broad EDA industry experience… Read More

Richard Goering does Q&A with ClioSoft CEO

Richard Goering is well-known from his editorial days at EE Times (going back some 25 years), now at Cadence he blogs at least once a week on EDA topics that touch Cadence tools.

Before DAC he talked with Srinath Anantharaman about how Cadence tools work together with ClioSoft tools to keep IC Design Data Management Simple.

Through… Read More