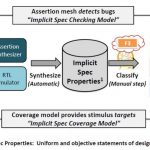

Assertion Synthesis is a new tool for verification and design engineers that can be used with simulation or emulation. At DVCon Yuan Lu of Atrenta is presenting a tutorial on Atrenta’s BugScope along with John Henri Jr of Cadence explaining how it helps emulation and Baosheng Wang of AMD discussing their experiences of the… Read More

Tag: eda

Cadence Sigrity, Together At Last

In July Cadence acquired Sigrity, one of the leaders in PCB and IC packaging analysis. Until a decade ago, signal integrity and power analysis was something that only IC designers needed to worry about. For all except the highest performance boards, relatively simple tools were sufficient. Provided you hooked up the pins on all… Read More

Another Winner at DesignCon

After a show like DesignConwraps up we get a chance to ask ourself what it all meant, and how was this year different than last year. Reading through many posts about DesignCon I came to discover that the Awards at DesignCon are less contentious than at CES, and also that ANSYSreceived a DesignVision awardfor the 2nd year running. … Read More

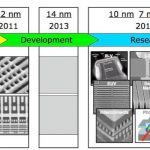

No EUV before 7nm?

I was at the Common Platform Technology Forum this week. One of the most interesting sessions is IBM’s Gary Patton giving an overview of the state of semiconductor fabrication. Then, at lunchtime, he is one of the people that the press can question. In this post, I’m going to focus on Extreme Ultra-Violet (EUV) lithography.… Read More

Sanjiv Kaul is New CEO of Calypto

Calypto announced that Sanjiv Kaul is the new CEO. I first met Sanjiv many years ago when he was still at Synopsys when I interviewed for a position there around the time I transitioned out of Compass and went back to the parent company VLSI. I forget what the position was. Then about three or four years ago when I did some work for Oasys… Read More

Software Driven Power Analysis

Power is a fundamentally hard problem. When you have finished the design, you have accurate power numbers but can’t do anything about them. At the RTL level you have some power information but it is often too late to make major architectural changes (add an offload audio-processor, for example). Early in the design, making… Read More

A Brief History of ClioSoft

In the 1990s, software developers were established users of software configuration management (SCM) tools such as open source RCS/CVS or of commercial systems such as Clearcase. Hardware designers, however, managed design data in ad hoc home-grown ways. ClioSoft’s founder, Srinath Anantharaman, recognized that hardware… Read More

Startups: the Biggest Challenge

What is the biggest challenge facing an EDA startup today? By a startup, I mean a brand new company, not a company that already has a few customers and is either on a fast path to success or a slower path whereby the company can continue to grow slowly forever.

Obviously, one challenge is the funding environment. Since EDA acquisitions… Read More

TSMC ♥ Oasys

Oasys has joined the TSMC Soft-IP Alliance Program. This means that TSMC IP partners have access to a new RTL exploration tool to improve QoR and reduce the iterations needed for design closure. In modern process nodes, RTL engineers implementing complex IP cores for graphics, networking, and mobile computing are struggling … Read More

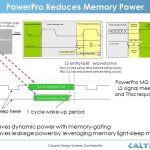

Dynamic/Leakage Power Reduction in Memories

Embedded memories have an important impact on power. SoCs that integrate multiple functions on a single silicon die are at the heart of many electronic devices. As process geometries have scaled, design teams have used more and more of the additional silicon real estate available to integrate embedded memories that serve as scratch-pads,… Read More