You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

I blogged last month about single event effects (SEE) where a semiconductor chip behaves incorrectly due to being hit by an ion or a neutron. Since we live on a radioactive planet and are bombarded by cosmic rays from space, this is a real problem, and it is getting worse at each process node. But just how big of a problem is it?

TFIT is … Read More

This year’s recipient of the Kaufman Award is Dr Chenming Hu. I can’t think of a more deserving recipient. He is the father of the FinFET transistor which is clearly the most revolutionary thing to come along in semiconductor for a long time. Of course he wasn’t working alone but he was the leader of the team at UC… Read More

Given the compressed time between 20nm and 16nm, twelve months versus the industry average twenty four months, it is time to start talking about 10nm, absolutely. Next Tuesday is the 19th annual TSMC Technology Symposium keynoted of course by the Chairman, Dr. Morris Chang.

Join the 2013 TSMC Technology Symposium. Get the latest… Read More

The burgeoning need of high density of electronic content on a single chip, thereby necessitating critical PPA (Power, Performance, Area) optimization, has pushed the technology node below 0.1 micron where static power becomes equally relevant as dynamic power. Moreover, multiple power rails run through the circuit at different… Read More

For three days in a couple of weeks time there is a crash of conferences, spread out all over the extended Bay Area.

Firstly, from 17-19th April at the Santa Clara Hyatt is the Linley Mobile Conference. This covers all things microprocessor in the mobile industry. Details of the conference including the full agenda are here. The conference… Read More

Sequential clock gating offers more power savings that can be obtained just with combinational clock gating. However, sequential clock gating is very complex as it involves temporal analysis over multiple clock cycles and examination of the stability, propagation, and observability of signal values.

Trying to do sequential… Read More

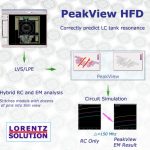

Accuracy, ease of use and performance have always been paramount for electromagnetic analysis software. Historically, it has been hard to find all three of these qualities in one tool. The result is that many high speed analog and RF designers resort to using multiple, often overlapping, tools to get the job done.

Lorentz Solution… Read More

Risks and Rewards of Engaging with EDA Startups:The Hunger Games!

Doing business with EDA startups comes with both risks and rewards. The Hogan’s Heroes panel at DAC 2013 features key decision makers from fabless, startup and vc firms sharing candid opinions on this risk/reward equation, and the financial and technical issues… Read More

In EDA we often talk about how fast a SPICE circuit simulator is, or about capacity and accuracy compared to silicon measurements. Yes, speed, capacity and accuracy are important, however when talking to actual transistor-level circuit designers you discover something quite different, most of their time is spent doing debugging,… Read More

Every quarter GSA runs a webinar with Dan Niles of Alpha One Capital Partners on what the semiconductor outlook is. He doesn’t actually focus on the semiconductor industry itself, demand for chips is really driven by economic conditions in the major markets around the world. People who are unemployed, or in Cyprus, don’t… Read More