There is a new book out from Springer. The subtitle is actually a better description that the title. The subtitle is A Practical Guide to Synopsys Design Constraints (SDC) but the title isConstraining Designs for Synthesis and Timing Analysis. The authors are Sridhar Gangadharan of Atrenta in San Jose and Sanjay Churiwala of Xilinx… Read More

Tag: eda

“NoC, NoC” – Are You Listening to nVidia’s Dally?

Recently Bill Dally, nVidia’s Chief Scientist & SVP of Research, and a professor of electrical engineering and computer science at Stanford University, has been out speaking quite a bit including a “short keynote” at the Design Automation Conference and a keynote at ISC 2013. The DAC audience is primarily EDA tool users and… Read More

Configurable System IP from a Tool Provider

While I have previously blogged on Forte’s Cynthesizer Workbench’s Interface Generator, I want to take another look from a different perspective. Watching the tool and IP together in action through public videos provided by Forte it struck me as odd what I did not consider earlier, on what should have been obvious to me – Forte is… Read More

How to Engage with the Fabless Semiconductor Ecosystem

SemiWiki is absolutely the best place to start of course. You can read observations, opinions, and experiences on a wide variety of semiconductor related topics from semiconductor professionals around the world. You can also mingle with the 653,105+ people who visit SemiWiki in the comment sections and the forum. Registration… Read More

VIA Adopts Cliosoft

VIA Telecom, who makes CDMA base-band processor chips, picked ClioSoft SOS for use by its analog mixed-signal design teams. Like many such teams they use Cadence’s Virtuoso layout platform. ClioSoft’s SOS is seamlessly integrated into Virtuoso so that designers don’t really need to spend much time worrying… Read More

Interview with Arasan

Recently I had a chance to chat with Arasan Ganesan, CEO at Arasan Chip Systems in San Jose, CA. Arasan Chip Systems has provided Silicon interface IP and supporting hardware and software to the semiconductor industry for more than 15 years. The headquarters are in San Jose and engineering offices in Bangalore and Tuticorin, India.… Read More

Data Centers accounts for 2 to 3% of WW Energy Consumption!

Do you think this figure will go down? Considering the massive move to Mobile equipment, pushing to de-localize your storage medium to instead use the cloud capabilities, and looking at the huge number of people buying smartphone and tablet in emerging countries, no doubt that Data Center related energy consumption is expected… Read More

Analysis of HLS Results Made Easier

In a recent article I discussed how easy it was to debug SystemC source code as shown in a video published on YouTube by Forte Design Systems. I also commented on the usefulness of the well-produced Forte video series. Today, I am reviewing another video in that series on analyzing high-level synthesis (HLS) results.

Cynthesizer… Read More

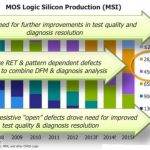

Towards the 0 DPM Test Goal

At Semicon yesterday I attended Mentor’s presentation on improving test standards. Joe Sawicki was meant to present but he was unable to get a flight due to the ongoing disruption at SFO after last weekend’s crash. I just flew in myself and it is odd to see the carcase of that 777 just beside the runway we landed on.

The … Read More

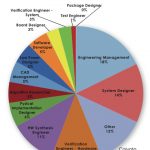

Calypto 2013 Report

Each year Calypto runs a survey of end-users. This year’s survey and report has two parts, power reduction and high level synthesis (HLS).

The topics covered are:

- survey methodology and demographics

- top methods used to reduce power

- engineering time spent on specfiic RTL tasks to reduce power

- plans to deploy RTL power reduction