In the early days of Atrenta I met with Ralph Marlett, a distinguished test expert with many years of experience at Zuken and Recal Redac. He talked me into believing we could do meaningful static analysis for DFT-friendliness at RTL. His work with us really opened my eyes to the challenges that test groups face in integrating their… Read More

Tag: dft

Getting Physical to Improve Test – White Paper

One of the most significant and oft repeated trends in EDA is the use of information from layout to help drive other parts of the design flow. This has happened with simulation and synthesis among other things. Of course, we think of test as a physical operation, but test pattern generation and sorting have been netlist based operations.… Read More

Novel DFT Approach for Automotive Vision SoCs

You may have seen a recent announcement from Mentor, a Siemens business, regarding the use of their Tessent DFT software by Ambarella for automotive applications. The announcement is a good example of how Mentor works with their customers to assure design success. On the surface the announcement comes across as a nice block and… Read More

Atos Crafts NoC, Pad Ring, More Using Defacto

I’ve talked before about how Defacto provides a platform for scripted RTL assembly. Kind of a rethink of the IP-XACT concept but without need to get into XML (it works directly with SV), and with a more relaxed approach in which you decide what you want to automate and how you want to script it.

They’re hosting a webinar on May 28th 10-11am… Read More

DFT Innovations Come from Customer Partnerships

There is an adage that says that quality is not something that can be slapped on at the end of the design or manufacturing process. Ensuring quality requires careful thought throughout development and production. Arguably this adage is more applicable to the topic of Design for Test (DFT) than almost any other area of IC development… Read More

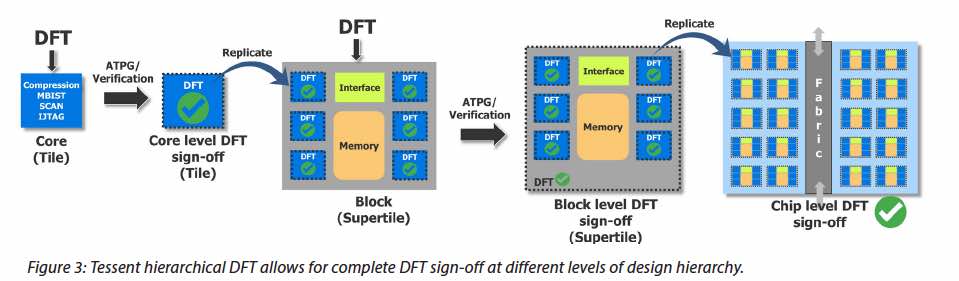

Bringing Hierarchy to DFT

Hierarchy is nearly universally used in the SoC design process to help manage complexity. Dealing with flat logical or physical designs proved unworkable decades ago. However, there were a few places in the flow where flat tools continued to be used. Mentor lead the pack in the years around 1999 in helping the industry move from … Read More

Can a hierarchical Test flow be used on a flat design?

It is pretty common for physical layout to work from a flattened hierarchy for blocks or even full chips, even though the front-end design starts with a hierarchical representation. This was not always the case. Way back when, the physical layout matched the logical hierarchy during the design process. Of course, this led to all… Read More

How to be Smart About DFT for AI Chips

We have entered the age of AI specific processors, where specialized silicon is being produced to tackle the compute needs of AI. Whether they use GPUs, embedded programmable logic or specialized CPUs, many AI chips are based on parallel processing. This makes sense because of the parallel nature of AI computing. As a result, in… Read More

The Pain of Test Pattern Bring-up for First Silicon Debug

In the semiconductor world we have divided our engineering talent up into many adjacent disciplines and each comes with their own job titles: Design engineers, Verification engineers, DFT engineers, Test engineers. When first silicon becomes available then everyone on the team, and especially management all have a few big … Read More

Mentor Tessent MissionMode Provides Runtime DFT for Self-Correcting Automotive ICs

The automotive industry continues push the limits on how “smart” we can make our vehicles and from that, it follows as to how smart we can make the electronics in the vehicles. When I think of smart cars (and smart automotive ICs) I typically think of things like advanced driver-assistance systems (ADAS) that use AI and neural networks… Read More